# CX93510 JPEG Encoder with a 656 Camera Interface and Optional Microphone Input

**Data Sheet**

DSH-202155B April 2010

### **Ordering Information**

| Model Number Description                |                                                  | Package                                         |  |  |  |  |  |  |

|-----------------------------------------|--------------------------------------------------|-------------------------------------------------|--|--|--|--|--|--|

| CX93510-11z*                            | 128 KByte buffer with Differential JPEG disabled | 48-pin eMLF/QFN, 6x6 mm Body. 0.5 mm Lead Pitch |  |  |  |  |  |  |

| CX93510-12z*                            | 256 KByte buffer with Differential JPEG enabled  |                                                 |  |  |  |  |  |  |

| *Lead-free (Pb Free) and RoHS compliant |                                                  |                                                 |  |  |  |  |  |  |

### **Revision History**

| Revision | Date            | Description            |  |

|----------|-----------------|------------------------|--|

| p1       | March 16, 2009  | Preliminary p1 release |  |

| p2       | July 31, 2009   | Preliminary p2 release |  |

| A        | October 8, 2009 | Revision A release     |  |

| В        | April 30, 2010  | Revision B release     |  |

© 2009, 2010, Conexant Systems, Inc. All Rights Reserved.

Information in this document is provided in connection with Conexant Systems, Inc. ("Conexant") products. These materials are provided by Conexant as a service to its customers and may be used for informational purposes only. Conexant assumes no responsibility for errors or omissions in these materials. Conexant may make changes to this document at any time, without notice. Conexant advises all customers to ensure that they have the latest version of this document and to verify, before placing orders, that information being relied on is current and complete. Conexant makes no commitment to update the information and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to its specifications and product descriptions.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Conexant's Terms and Conditions of Sale for such products, Conexant assumes no liability whatsoever.

THESE MATERIALS ARE PROVIDED "AS IS" WITHOUT WARRANTY OF ANY KIND, EITHER EXPRESS OR IMPLIED, RELATING TO SALE AND/OR USE OF CONEXANT PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, CONSEQUENTIAL OR INCIDENTAL DAMAGES, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. CONEXANT FURTHER DOES NOT WARRANT THE ACCURACY OR COMPLETENESS OF THE INFORMATION, TEXT, GRAPHICS OR OTHER ITEMS CONTAINED WITHIN THESE MATERIALS. CONEXANT SHALL NOT BE LIABLE FOR ANY SPECIAL, INDIRECT, INCIDENTAL, OR CONSEQUENTIAL DAMAGES, INCLUDING WITHOUT LIMITATION, LOST REVENUES OR LOST PROFITS, WHICH MAY RESULT FROM THE USE OF THESE MATERIALS.

Conexant products are not intended for use in medical, lifesaving or life sustaining applications. Conexant customers using or selling Conexant products for use in such applications do so at their own risk and agree to fully indemnify Conexant for any damages resulting from such improper use or sale.

The following are trademarks of Conexant Systems, Inc.: Conexant<sup>®</sup> and the Conexant C symbol. Product names or services listed in this publication are for identification purposes only, and may be trademarks of third parties. Third-party brands and names are the property of their respective owners.

For additional disclaimer information, please consult Conexant's Legal Information posted at www.conexant.com which is incorporated by reference.

Conexant Lead-free products are China RoHS Compliant:

Reader Response: Conexant strives to produce quality documentation and welcomes your feedback. Please send comments and suggestions to tech.pubs@conexant.com. For technical questions, contact your local Conexant sales office or field applications engineer.

#### Preliminary Information

This document contains information on a new product. The parametric information, although not fully characterized, is the result of testing initial devices.

# CX93510 JPEG Encoder with a 656 Camera Interface and Optional Microphone Input

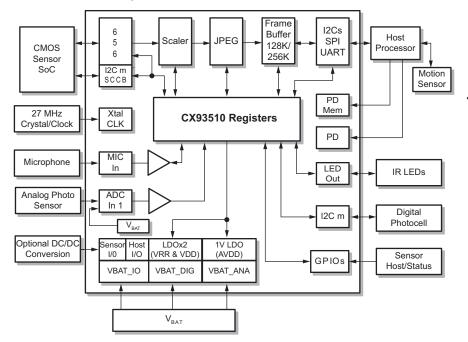

The CX93510 is a monolithic mixed signal Application-Specific Standard Product (ASSP) designed for low cost and low power motion detection surveillance camera applications. Used with an external CMOS image sensor, the CX93510 can compress and store several images in an internal 256KB/128KB frame buffer. An optional 2:1 scaler can provide Quarter Video Graphics Array (QVGA) images from the VGA input. With a microphone input and

4 KB of optionally allocated buffering, a 2- or 4-bit ADPCM audio session can be recorded simultaneously during image captures. The stored images and audio data are then passed on to an external microprocessor for uploading to a desired medium. The CX93510 is controlled through a simple register set via the microprocessor interface, and the variety of available interfaces (Serial Peripheral Interface [SPI], UART, and I<sup>2</sup>C) allow for wide flexibility in microprocessor selection. With both digital and analog photocell sensor inputs available, the CX93510 can facilitate the measurement of ambient light and use an on-chip LED driver to control an external infrared LED during low-light conditions. With low cost and low power, the CX93510 is ideally suited for security applications requiring visual verification.

#### **Functional Block Diagram**

#### **Distinguishing Features**

- Supported Applications and operating Modes

- PIR Sensor with Video

- ✓ Visual verification of intruder via image sensor interface

- ✓ VGA B&W or Color @ up to 30 fps

- ✓ VGA to QVGA Filtered ½ res Scaling

- ✓ JPEG & MJPEG-DPCM Image Compression (ISO/IEC 10918-1/2)

- ✓ Differential JPEG Mode

- ✓ Continuous streaming and variable image modes

- ✓ 256 KB or 128 KB frame buffer for compressed images (no external memory)

- ✓ Interface to external µP though SPI, UART, or I<sup>2</sup>C

- Variable IR illumination control port

- ✓ A/D for Photocell sensor, Battery voltage monitor, or microphone inputs

- ✓ Sleep mode SoC off except frame buffer in retention mode

- Video Intercom/Door Phone

- Baby monitor applications

- Remote home monitoring

- Interfaces

- Sensor i/f

✓ 8-b 4:2:2 YCbCr with BT-656 embedded timing codes or frame/line sync support up to 27 MHz, progressive mode

- ✓ Resolutions: VGA (640x480) & QVGA (320x240)

- ✓ 27 MHz clk output

- ✓ 2/3 wire control i/f: I<sup>2</sup>C Master port or SCCB

- 4-wire I2C/SPI/UART slave port to external μP

- 8 GPIO (5 dedicated pins, 3 shared pins)

- IR illumination with variable DAC and PWM control

- Microphone input, mic boost 0-36 dB in 6 dB steps, 2- and 4- bit ADPCM

- DC measurement battery monitor

- Photocell sensor input analog or I<sup>2</sup>C (shared with GPIO)

- Support for battery operation: 3.6 V to 1.8 V

- ◆ 48-pin eMLF/QFN

- 10 °C to +85 °C ambient, +100 °C junction

- 12 mA in operational mode

- 10 nA in sleep mode

# Contents

| Figu  | res                             |                                                                                                                                                                                                                                                                                                   | . 9                                                |

|-------|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| Table | es                              |                                                                                                                                                                                                                                                                                                   | 11                                                 |

| 1     | Ove                             | rview                                                                                                                                                                                                                                                                                             | 13                                                 |

|       | 1.1<br>1.2<br>1.3<br>1.4<br>1.5 | Passive Infrared Security System         Power Supplies         Voltage Regulators         Power Management         Power Modes         1.5.1       Sleep Mode         1.5.2       Idle Mode         1.5.3       Active Mode         1.5.4       Retention Mode         Crystal Input       Reset | 14<br>14<br>15<br>18<br>18<br>18<br>18<br>18<br>18 |

| 2     |                                 | Description                                                                                                                                                                                                                                                                                       |                                                    |

|       |                                 |                                                                                                                                                                                                                                                                                                   |                                                    |

| 3     | Elec                            | strical Specifications                                                                                                                                                                                                                                                                            | 23                                                 |

|       | 3.1<br>3.2<br>3.3<br>3.4        | Absolute Maximum Ratings<br>DC Characteristics and Operating Conditions<br>Analog Characteristics<br>Timing Specifications                                                                                                                                                                        | 23<br>24                                           |

| 4     | Sen                             | sor Interface                                                                                                                                                                                                                                                                                     | 27                                                 |

|       | 4.1                             | Supported Resolutions and Frame/Data Rates                                                                                                                                                                                                                                                        |                                                    |

|       | 4.2                             | Supported Data Formats.         4.2.1       YCbCr 4:2:2.         4.2.2       Monochrome (Y Only)                                                                                                                                                                                                  | 27                                                 |

|       | 4.3<br>4.4                      | Continuous vs. Limited Frame Mode                                                                                                                                                                                                                                                                 | 28<br>28                                           |

|       | 4.5<br>4.6<br>4.7               | 4.4.1       Discrete Timing Mode         Embedded Timing Mode                                                                                                                                                                                                                                     | 29<br>30                                           |

|       | 4.8                             | Sensor Control Interface                                                                                                                                                                                                                                                                          | 30                                                 |

|   |                  | 4.8.2 SCCB                                                                               |

|---|------------------|------------------------------------------------------------------------------------------|

|   | 4.9              | Miscellaneous Interface Controls                                                         |

|   | 4.10             | Usage Scenarios                                                                          |

|   |                  | 4.10.1 Limited/Single Frame Mode                                                         |

|   |                  | 4.10.2 Continuous Frame Mode                                                             |

| 5 | Vid              | eo/Image Processing                                                                      |

|   | 5.1              | Format and Scaling                                                                       |

|   | 5.2              | Bandwidth and Storage Requirements                                                       |

|   |                  | 5.2.1 Storage of Compressed Images                                                       |

|   | 5.3              | Frame Buffer                                                                             |

|   |                  | 5.3.1 Frame Buffer Overview                                                              |

|   |                  | 5.3.2 Frame Buffer Memory Map and Format                                                 |

|   |                  | 5.3.3 Configuration Data                                                                 |

|   |                  | 5.3.4 Frame Buffer Full                                                                  |

| 6 | Ima              | ge Compression                                                                           |

|   | 6.1              | JPEG Controller                                                                          |

|   | 6.2              | MJPEG-DPCM                                                                               |

|   | 6.3              | Reconstruction of Frame Data                                                             |

|   | 6.4              | Mathematical Equations                                                                   |

|   | 6.5              | Differences Between Reference and Difference Frames                                      |

| 7 | μ <mark>Ρ</mark> | and Miscellaneous Interfaces                                                             |

|   | 7.1              | μP Interface                                                                             |

|   |                  | 7.1.1 SPI Timing                                                                         |

|   |                  | 7.1.2 I <sup>2</sup> C Timing                                                            |

|   |                  | 7.1.3 UART Timing and Protocol                                                           |

|   | 7.2              | GPIO                                                                                     |

|   | 7.3              | ADPCM                                                                                    |

|   |                  | 7.3.1         Block Size         56           7.3.2         Monaural Preamble         57 |

|   | 7.4              | 7.3.2       Monaural Preamble       57         Register Interface       58               |

|   | 7.5              | Host Frame Buffer Interface                                                              |

|   |                  | 7.5.1 Host Serial Interface Bandwidth                                                    |

|   |                  | 7.5.2 Frame Buffer Access                                                                |

|   |                  | 7.5.3 ADPCM Output to Frame Buffer                                                       |

|   |                  | 7.5.3.1 Audio Stop                                                                       |

|   |                  | Zero Padding 61                                                                          |

|   |                  | Requirement for STOP 61                                                                  |

|   |                  | Audio Flow                                                                               |

|   |                  | Summary of Audio Flow Requirements                                                       |

|   |                  | 7.5.4 Host Write to Frame Buffer                                                         |

|   |                  | 7.5.5 Debug and ADPCM bypass mode                                                        |

| 8 | Ana              | log Interfaces                                                                           |

|   | 8.1              | Microphone Input                                                                         |

|   | 8.2              | Battery Monitor                                                                          |

|   |                  |                                                                                          |

|   |     | 8.2.1              | Equation for Battery Monitoring                         | 65   |

|---|-----|--------------------|---------------------------------------------------------|------|

|   | 8.3 |                    | cell Sensor Input                                       |      |

|   | 8.4 | IR Illur           | mination                                                | . 67 |

| 9 | Reg | jisters.           |                                                         | 71   |

|   | 9.1 | Senso              | r Interface                                             | . 71 |

|   |     | 9.1.1              | Sensor Interface Configuration                          | . 71 |

|   |     | 9.1.2              | Horizontal Active                                       | . 72 |

|   |     | 9.1.3              | Horizontal Capture Delay                                | . 72 |

|   |     | 9.1.4              | Horizontal Capture Width                                | . 73 |

|   |     | 9.1.5              | Vertical Active                                         | . 73 |

|   |     | 9.1.6              | Vertical Capture Delay                                  | . 73 |

|   |     | 9.1.7              | Vertical Capture Height                                 | . 73 |

|   |     | 9.1.8              | I2C/SCCB Device Address                                 | . 74 |

|   |     | 9.1.9              | I2C/SCCB Address                                        | . 74 |

|   |     | 9.1.10             | I2C/SCCB Read/Write Data - Low Byte                     | . 74 |

|   |     | 9.1.11             | I2C/SCCB Read/Write Data - High Byte                    | . 75 |

|   |     |                    | I2C Control.                                            |      |

|   |     |                    | Filter Config                                           |      |

|   | 9.2 |                    | Controller                                              |      |

|   |     | 9.2.1              | MJPEG-DPCM Control                                      |      |

|   |     | 9.2.2              | JPEG Encoder Status                                     |      |

|   |     | 9.2.3              | JPEG Decoder Status                                     |      |

|   | 9.3 |                    | nterface                                                |      |

|   |     | 9.3.1              | Slave Select Control                                    |      |

|   |     | 9.3.2              | Frame Buffer 18-b Address                               |      |

|   |     | 9.3.3              | Error Status                                            |      |

|   |     | 9.3.4              | Host Interface Enable to Write to FB                    |      |

|   |     | 9.3.5              | Write/Read Data From/To host.                           |      |

|   |     | 9.3.6              | Audio Buffer Status                                     |      |

|   |     | 9.3.7              | Audio Buffer Read Pointer                               |      |

|   |     | 9.3.8              | Audio Byte Count                                        |      |

|   |     |                    | ADPCM No. of Samples (10-bit value MIN = 32, MAX = 512) |      |

|   |     |                    |                                                         |      |

|   |     |                    | Photocell Output and Battery Monitor (16 Bits)          |      |

|   |     |                    | GPIO Inputs                                             |      |

|   |     |                    | GPIO Outputs                                            |      |

|   |     |                    | GPIO Output Enables                                     |      |

|   | 9.4 |                    |                                                         |      |

|   | 3.4 | 9.4.1              | Microphone and Auxiliary ADC                            |      |

|   |     | 9.4.1              | LED Driver                                              |      |

|   |     | 9.4.2              | Regulator for Analog Supply                             |      |

|   |     | 9.4.3<br>9.4.4     | Regulator for Digital and RAM Supplies                  |      |

|   |     | 9.4.4              | Regulator for RAM Supply - Retention Mode.              |      |

|   |     | 9.4.5              | ADC Decimation Parameters                               |      |

|   |     | 9.4.0<br>9.4.7     | LED PWM Control                                         |      |

|   |     | J. <del>4</del> .1 |                                                         | . 31 |

|    |      | 9.4.8 LED ON_DELAY                  | 91 |

|----|------|-------------------------------------|----|

|    | 9.5  | Extended Temperature Considerations | 92 |

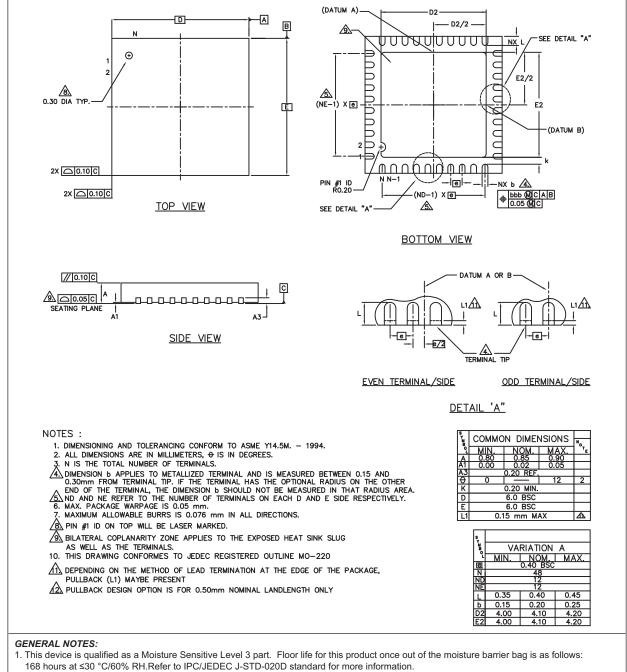

| 10 | Pac  | kage Diagrams                       | 93 |

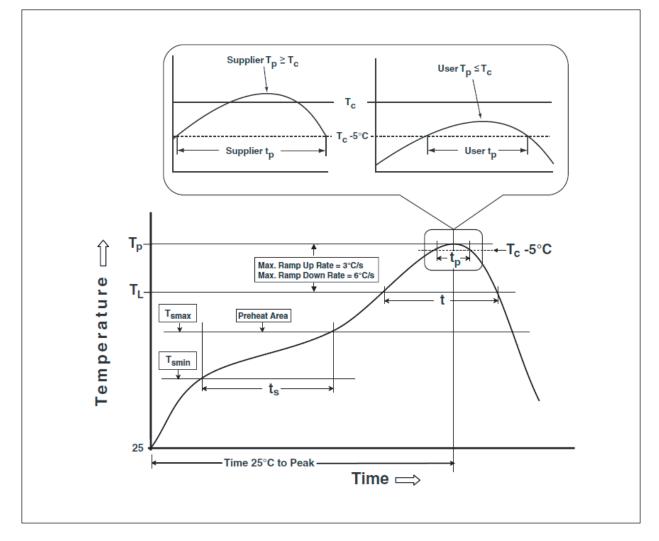

|    | 10.1 | Reflow Profile                      | 94 |

# Figures

| Figure 1.  | PIR Sensor with Visual Verification System Block Diagram  | 13 |

|------------|-----------------------------------------------------------|----|

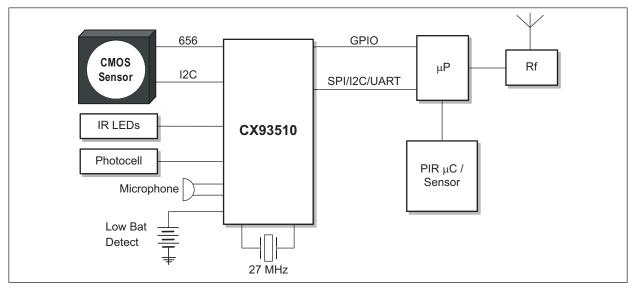

| Figure 2.  | Basic Configuration                                       | 15 |

| Figure 3.  | CMOS Sensor Runs on Battery Voltage                       | 16 |

| Figure 4.  | External DC/DC Converter for Core Supplies                | 17 |

| Figure 5.  | Pin Diagram                                               | 21 |

| Figure 6.  | Example Device Interface Connections                      | 22 |

| Figure 7.  | Discrete Timing Mode                                      | 28 |

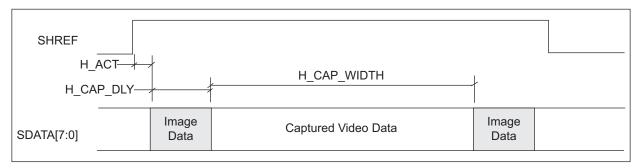

| Figure 8.  | Typical Video Data Capture                                | 29 |

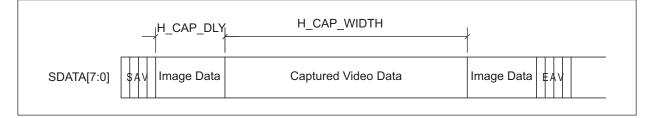

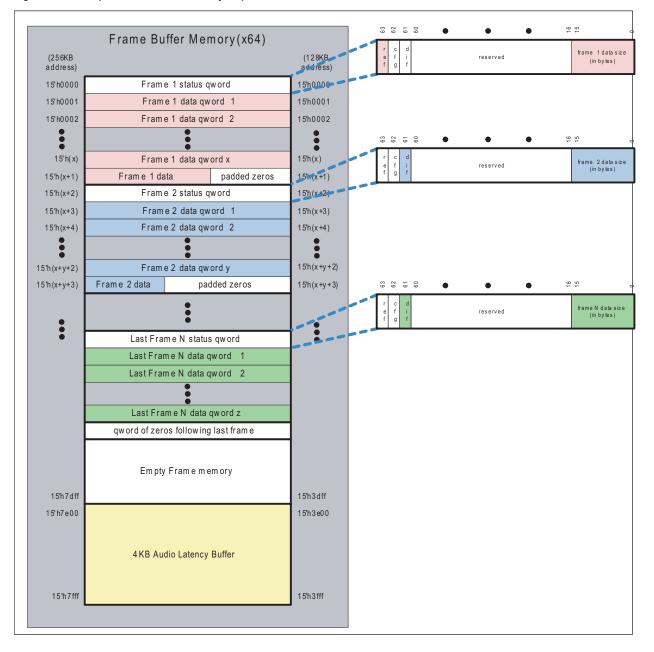

| Figure 9.  | Example Frame Buffer Memory Map with Audio Buffer Enabled | 38 |

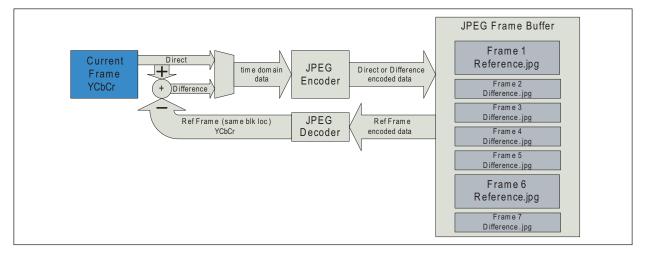

| Figure 10. | MJPEG Differential Encoding Algorithm                     | 42 |

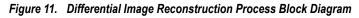

| Figure 11. | Differential Image Reconstruction Process Block Diagram   | 43 |

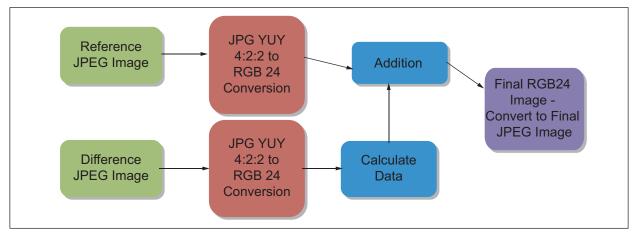

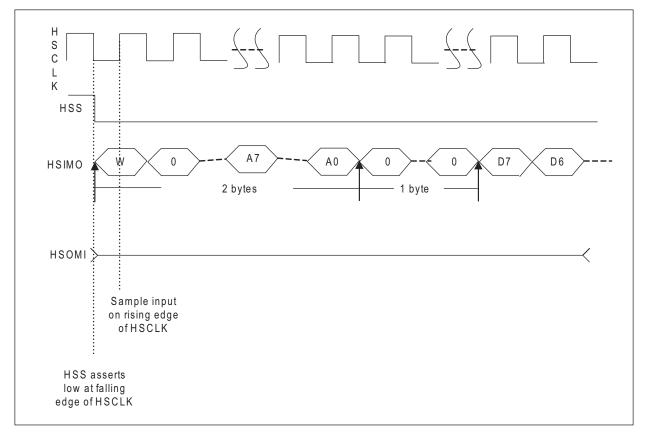

| Figure 12. | SPI Read Timing                                           | 48 |

| Figure 13. | SPI Write Timing                                          | 49 |

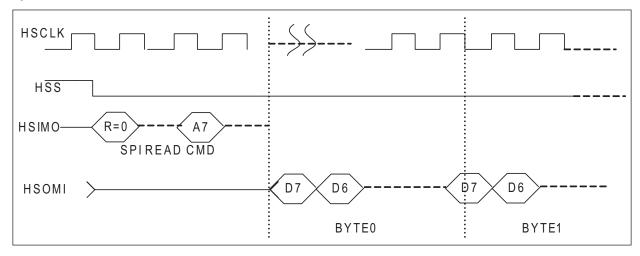

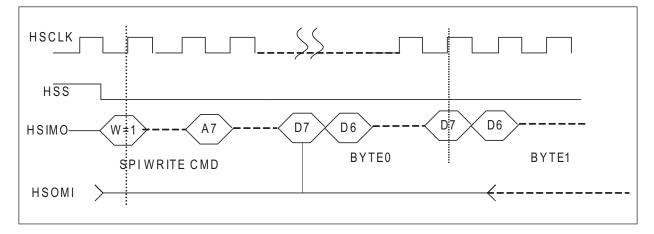

| Figure 14. | SPI Burst Read                                            | 49 |

| Figure 15. | SPI Burst Write                                           | 50 |

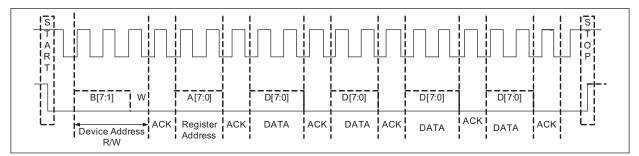

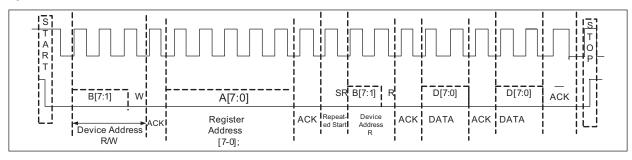

| Figure 16. | Write Transaction in I <sup>2</sup> C                     | 51 |

| Figure 17. | Read Transaction in I <sup>2</sup> C                      | 51 |

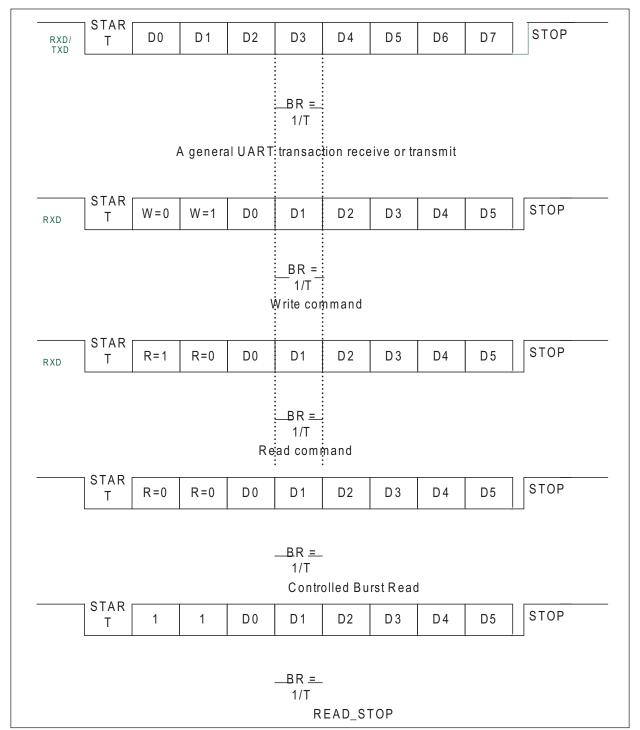

| Figure 18. | A Typical UART Transaction (T = 1MHz)                     | 53 |

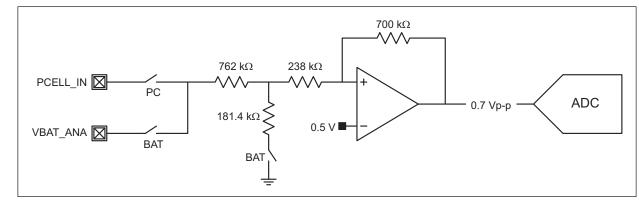

| Figure 19. | ADC Internal Path                                         | 65 |

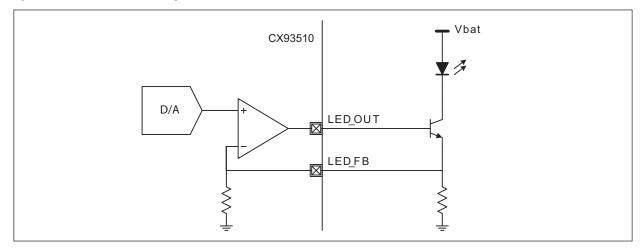

| Figure 20. | Driver Output Waveform                                    | 68 |

| Figure 21. | Current Source Configuration                              | 68 |

| Figure 22. | Voltage Source Configuration                              | 69 |

| Figure 23. | Package Diagram                                           |    |

| Figure 24. | Classification Profile                                    | 95 |

|            |                                                           |    |

# Tables

| Pin Descriptions.                                                  | 19                                                                                                                                                                                                                                                                                                                                |

|--------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                    |                                                                                                                                                                                                                                                                                                                                   |

|                                                                    |                                                                                                                                                                                                                                                                                                                                   |

| Analog Characteristics                                             |                                                                                                                                                                                                                                                                                                                                   |

| Timing Specifications.                                             | 25                                                                                                                                                                                                                                                                                                                                |

| SAV and EAV Packets                                                | 29                                                                                                                                                                                                                                                                                                                                |

| SCCB Signals                                                       | 31                                                                                                                                                                                                                                                                                                                                |

| Size and Number of Images for 256 KB Frame Buffer                  |                                                                                                                                                                                                                                                                                                                                   |

| Basic JPEG Frame Format                                            | 36                                                                                                                                                                                                                                                                                                                                |

| Differences Between Reference and Difference Frames                | 44                                                                                                                                                                                                                                                                                                                                |

| Pin Muxing.                                                        | 45                                                                                                                                                                                                                                                                                                                                |

| Host Serial Interface Streaming Rate for Various Compression Modes | 58                                                                                                                                                                                                                                                                                                                                |

| Driver Output Based on 6-Bit Setting                               | 67                                                                                                                                                                                                                                                                                                                                |

| Classification Reflow Profile                                      | 94                                                                                                                                                                                                                                                                                                                                |

|                                                                    | Timing Specifications.<br>SAV and EAV Packets<br>SCCB Signals<br>Size and Number of Images for 256 KB Frame Buffer<br>Basic JPEG Frame Format<br>Differences Between Reference and Difference Frames<br>Pin Muxing.<br>Host Serial Interface Streaming Rate for Various Compression Modes<br>Driver Output Based on 6-Bit Setting |

**Overview**

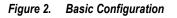

# 1.1 Passive Infrared Security System

Figure 1 illustrates a Typical Passive Infrared (PIR) security system with video and audio verification. Upon a motion event, the host processor wakes and configures the CX93510 in preparation for image/audio captures. Depending on the selected CMOS sensor, the system should be able to wake, measure ambient light conditions, configure the CMOS sensor, illuminate the IR LEDs for low light conditions, and begin image/audio captures within 100 ms of motion being detected.

As the image and audio data are acquired, both are compressed and stored in the internal 256 KB (or 128 KB option) frame buffer. Depending on the selected device, image data is encoded using JPEG or MJPEG\_DPCM (Differential JPEG). Audio data is compressed into 4-bit ADPCM format, or a non-standard 2-bit ADPCM for maximum compression. In a typical scenario the host will read the contents of the frame buffer and send the information over an RF link to a base station where the image and audio data can be sent to desired location such as a cell phone, email address, or security service.

For systems that are battery powered, the CX93510 can operate between 3.3 V and 1.8 V. To conserve power, it can also remain in a very deep sleep during idle periods, essentially maintaining an off state until awakened by the host processor. Should the host not want to download the data immediately, an optional memory retention setting can be enabled to save the contents of the frame buffer while the rest of the device is shut down. A battery measurement input allows the host to monitor the battery level and alert the user if battery replacement is needed. Most CMOS sensors have one or more power supply feeds, of which some cannot drop too low in voltage. In these situations, the sensor and the sensor I/O on the CX93510 can be powered using a DC-DC buck-boost converter, which can be controlled using a GPIO from the CX93510. Refer to the following sections for more details on the available power options and configurations.

# 1.2 **Power Supplies**

The nominal core power supply is  $0.8 \text{ V} (\pm 5\%)$

The nominal AFE power supply is  $1.0 V (\pm 5\%)$

The nominal I/O power supply is 3.3 V with a package pin specification of 3.47 V maximum, and 1.8 V minimum.

During normal active functional mode, power-savings modes, or clock-gating are used for non-active components, interfaces, or functions. The frame buffer is on its own supply system in order to support memory retention during sleep mode.

There are two I/O power supplies: VDDO1 and VDDO2. All the image sensor I/F pins are connected to VDDO2, and the digital I/O pins (host I/F, GPIO, test, etc.) are connected to VDDO1. Each can be at a different voltage.

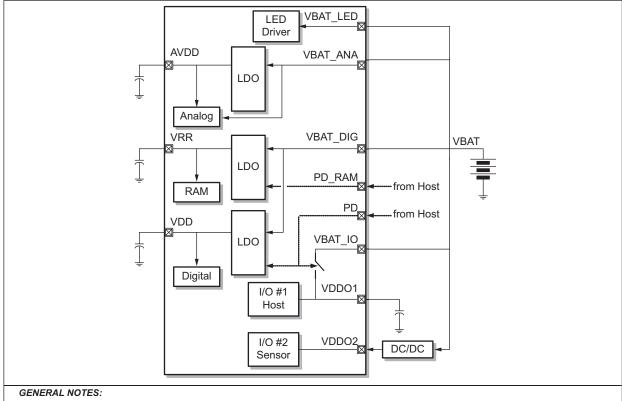

# 1.3 Voltage Regulators

The CX93510 includes three internal linear voltage regulators that generate:

- 1.0 V supply for all analog circuitry

- 0.8 V supply for the digital core

- 0.8 V supply for the RAM

Each supply voltage can be adjusted independently by register bits. Also the analog regulator can be enabled/disabled by a register bit, while the digital and RAM regulators are enabled/disabled via the power on VBAT\_DIG.

All supplies must be externally decoupled with a 1  $\mu$ F capacitor.

The user can choose to not use one or more internal regulators; in that case, the regulator input should be left unconnected or grounded. The output power pin can then be connected to an external power source. Note that VBAT\_DIG, if connected, powers both the RAM and Digital regulators. See power management diagrams below.

Each regulator provides a POR (power-on reset) signal that goes to logic high when its output has reached a given percentage (typ 95 percent) of its final target.

# 1.4 Power Management

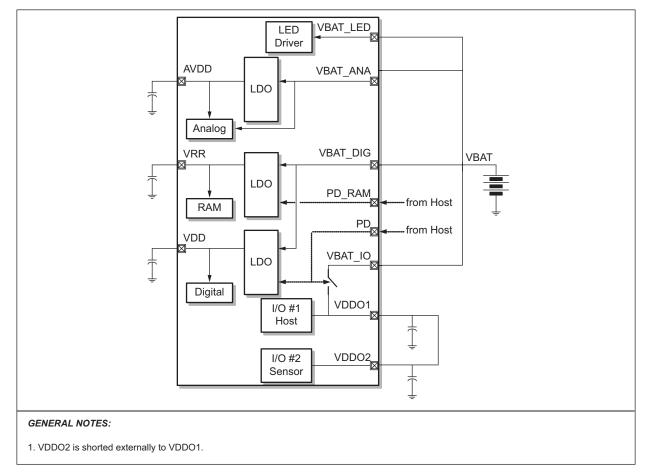

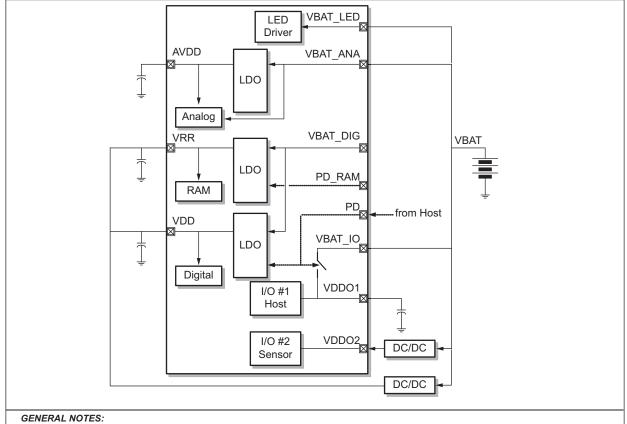

With the availability of internal voltage regulators and I/O connection options, the CX93510 allows for flexible power management options. A few examples are shown in Figures 2 through 4.

1. Internal LDOs used for all core voltages.

2. PD pin controls VDD and VDDO1 rails.

3. Sensor interface is powered by external DC/DC converter; VDDO2 rail uses the same power rail.

4. If using a DC-DC converter to power VDDO2, gate its enable pin with the PD enable pin such that the converter will shut down when PD

is driven low. In other words, VDDO2 should be shut down whenever the device is put to sleep.

#### Figure 3. CMOS Sensor Runs on Battery Voltage

#### Figure 4. External DC/DC Converter for Core Supplies

1. VBAT\_DIG pin is left unconnected; internal regulators for VDD and VRR are disabled.

2. PD\_RAM pin status is not relevant.

3. PD pin controls only VDDO1 rail.

4. If using a DC-DC converter to power VDDO2, gate its enable pin with the PD enable pin such that the converter will shut down when PD is driven low.

# 1.5 Power Modes

For most applications the CX93510 will be in Sleep power mode > 99% of the time. When an event occurs, the external  $\mu$ P will awaken the CX93510 causing it to enter Idle mode as registers are loaded and the CMOS image sensor is setup. As a series of images are captured, the CX93510 will alternate between Active and Idle power modes. If the host does not wish to immediately retrieve the images but there is a desire to retain the captured images, Retention power mode can be enabled.

The following power modes are referred to within this document:

### 1.5.1 Sleep Mode

The CX93510 is powered off. There is zero current except for that used by the PD and PD\_RAM pins to monitor the wakeup condition. All the I/O and core logic and SRAMS are powered off.

### 1.5.2 Idle Mode

Audio and Video processing are clock gated off. The only activity is the host interface read/write to registers or frame buffer access, and sensor i/f r/w register access.

### 1.5.3 Active Mode

Full activity consisting of video capture, JPEG encoding, and/or audio encoding.

### 1.5.4 Retention Mode

The CX93510 is powered off except for the configured portion of the frame buffer maintaining its memory state.

## 1.6 Crystal Input

The CX93510 clock input is from an attached 27 MHz crystal or clock source with a tolerance of 100 ppm. The clock source should have a 50 percent duty cycle,  $\pm$ 10 percent.

### 1.7 Reset

The CX93510 is reset automatically upon power-up on the VBAT\_DIG pin or power applied at the VDD pin if using an external power source. The internal LDO will in turn provide a reset signal to the device.

# **Pin Description**

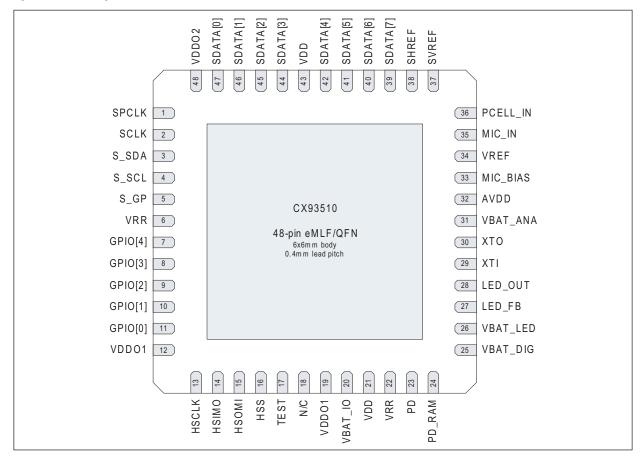

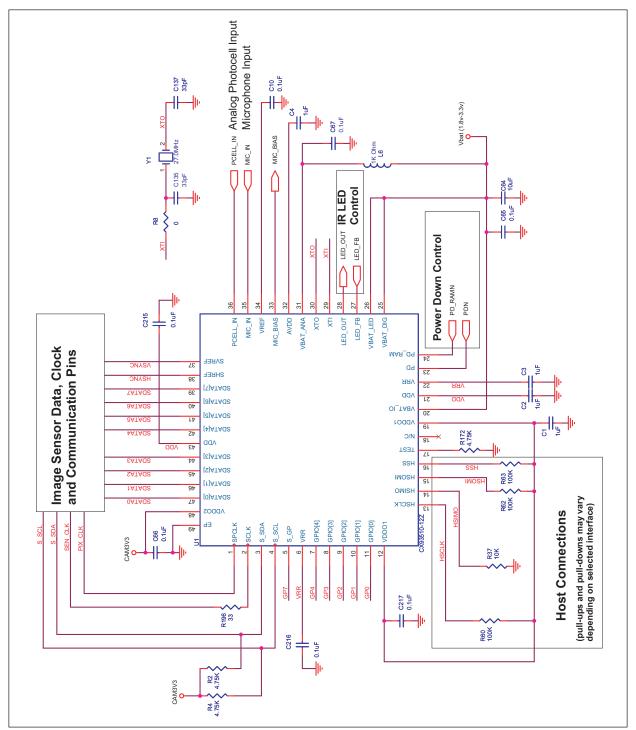

The pins and their functions are listed in Table 1. Figure 5 provides a pin diagram, and Figure 6 provides an example schematic of the device interface connections.

#### Table 1.Pin Descriptions (1 of 2)

| Pin Name         | Dir | Pin Number | Description                                                                                                              |  |  |  |  |  |

|------------------|-----|------------|--------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Analog Front End |     |            |                                                                                                                          |  |  |  |  |  |

| MIC_IN           | I   | 35         | Microphone input.                                                                                                        |  |  |  |  |  |

| MIC_BIAS         | 0   | 33         | Microphone bias.                                                                                                         |  |  |  |  |  |

| VREF             | 0   | 34         | Decoupling cap for common-mode voltage reference. Use a 0.1 $\mu\text{F}$ capacitor.                                     |  |  |  |  |  |

| XTI              | I   | 29         | 27.0 MHz crystal oscillator input, or single-ended clk.                                                                  |  |  |  |  |  |

| ХТО              | 0   | 30         | Crystal buffer output.                                                                                                   |  |  |  |  |  |

| PCELL_IN         | I   | 36         | Analog Photocell input. (0-1V)                                                                                           |  |  |  |  |  |

| PD               | I   | 23         | Power-down (=0). Enable (=1) signal for PIR ckts.                                                                        |  |  |  |  |  |

| PD_RAM           | I   | 24         | Power-down RAM. Enable for image retention buffer.                                                                       |  |  |  |  |  |

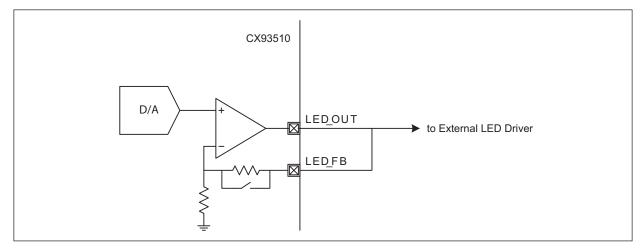

| LED_OUT          | 0   | 28         | IR LED driver output.                                                                                                    |  |  |  |  |  |

| LED_FB           | I   | 27         | IR LED driver feedback signal.                                                                                           |  |  |  |  |  |

| AVDD             | I/O | 32         | 1.0 V power supply for AFE. Connect 1 $\mu F$ capacitor to ground.                                                       |  |  |  |  |  |

| VBAT_DIG         | I   | 25         | Battery voltage to VDD and VRR regulators.                                                                               |  |  |  |  |  |

| VBAT_IO          | I   | 20         | Battery voltage to I/O power switch.                                                                                     |  |  |  |  |  |

| VBAT_ANA         | I   | 31         | Battery voltage to analog and AVDD regulator.                                                                            |  |  |  |  |  |

| VBAT_LED         | I   | 26         | Battery voltage to LED driver.                                                                                           |  |  |  |  |  |

|                  |     | Dię        | gital Power Supply                                                                                                       |  |  |  |  |  |

| VDD              | I/O | 21, 43     | Digital Standard Cell Core Power. 0.8 V nominal. Connect both pins together and add 1 $\mu\text{F}$ capacitor to ground. |  |  |  |  |  |

| VRR              | I/O | 6, 22      | Digital Frame Buffer Core Power. 0.8 V nominal. Connect both pins together and add 1 $\mu\text{F}$ capacitor to ground   |  |  |  |  |  |

| VDDO1            | 0   | 12, 19     | Pad Ring Power.<br>3.3 V nominal. Connect both pins together and add 1 $\mu$ F capacitor to ground.                      |  |  |  |  |  |

| VDDO2            | I   | 48         | Pad Ring Power.<br>3.3 V nominal.                                                                                        |  |  |  |  |  |

#### Table 1.Pin Descriptions (2 of 2)

| Pin Name Dir Pin Number Description       |                                                  |         |                                                                                    |  |  |  |

|-------------------------------------------|--------------------------------------------------|---------|------------------------------------------------------------------------------------|--|--|--|

|                                           | I                                                | Ge      | eneral Purpose I/O                                                                 |  |  |  |

| GPIO[4:0] I/O 7, 8, 9, 10, 11             |                                                  |         | 5-b General purpose I/O port. GPIO[4:3] may be used for optional photocel I2C i/f. |  |  |  |

|                                           | L.                                               | :       | Sensor Interface                                                                   |  |  |  |

| SDATA[7:0]                                | DATA[7:0] I 39, 40, 41,<br>42, 44, 45,<br>46, 47 |         |                                                                                    |  |  |  |

| SVREF                                     | I/O                                              | 37      | Frame (Vertical Active) indicates active region of frame, or GPIO[5]               |  |  |  |

| SHREF                                     | I/O                                              | 38      | Line (Horizontal Active) indicates active region of line, or GPIO[6]               |  |  |  |

| SPCLK                                     | I                                                | 1       | Pixel clock – up to 27 MHz; used to sample above signals                           |  |  |  |

| SCLK                                      | 0                                                | 2       | 27 MHz Clock output to Sensor.                                                     |  |  |  |

| S_SCL                                     | I/O                                              | 4       | I2C Serial Clock or SCCB SIO_C                                                     |  |  |  |

| S_SDA I/O 3 I2C Serial Data or SCCB SIO_D |                                                  |         |                                                                                    |  |  |  |

| S_GP                                      | I/O                                              | 5       | SCCB_E or GPIO[7].                                                                 |  |  |  |

|                                           | 1                                                | Host mP | Slave SPI/I2C/UART Port                                                            |  |  |  |

| HSCLK                                     | I/O                                              | 13      | Serial Clock (or SCL or TxD)                                                       |  |  |  |

| HSIMO                                     | I/O                                              | 14      | Serial Data input (or RTS)                                                         |  |  |  |

| HSOMI                                     | I/O                                              | 15      | Slave Output (or SDA or CTS)                                                       |  |  |  |

| HSS                                       | I                                                | 16      | Slave select (I2C adr sel or RxD)                                                  |  |  |  |

|                                           | I                                                | Misce   | llaneous Chip Control                                                              |  |  |  |

| TEST                                      | I                                                | 17      | Test Mode (tie low for normal operation).                                          |  |  |  |

| Reserved                                  |                                                  |         | Reserved                                                                           |  |  |  |

| Reserved                                  |                                                  |         | Reserved                                                                           |  |  |  |

| Reserved                                  |                                                  |         | Reserved                                                                           |  |  |  |

| Reserved                                  |                                                  |         | Reserved                                                                           |  |  |  |

1. The exposed ground pad serves as the only ground reference and must be properly grounded. All internal grounds are down-bonded to this pad.

2. Add 1 µF decoupling capacitors near VDDO1, VDD, VRR, and AVDD (pins 19, 21, 22, and 32 respectively).

3. The CX93510 must see at least three rising edges of SPCLK before it is able to detect the first SVREF edge and capture the first frame.

#### Figure 5. Pin Diagram

#### Figure 6. Example Device Interface Connections

# **Electrical Specifications**

# 3.1 Absolute Maximum Ratings

Absolute maximum ratings are listed in Table 2, DC characteristics and operating conditions are listed in Table 3, analog characteristics are listed in Table 4, and timing specifications are listed in Table 5.

#### Table 2. Absolute Maximum Ratings

| Parameter                                                                                  | Minimum | Maximum  | Unit |

|--------------------------------------------------------------------------------------------|---------|----------|------|

| 3.3 V supplies                                                                             | -0.3    | 4.2      | V    |

| 1.0 V supply <sup>(1)</sup>                                                                | -0.3    | 1.2      | V    |

| 0.8 V supplies <sup>(1)</sup>                                                              | -0.3    | 1.2      | V    |

| Voltage on any signal pin                                                                  | -0.3    | Vdd+ 0.3 | V    |

| Storage Temperature                                                                        | -65     | 150      | °C   |

| <i>FOOTNOTES:</i> <sup>(1)</sup> With regulators turned off and power supplied externally. |         |          |      |

# 3.2 DC Characteristics and Operating Conditions

| Parameter                       | Direction        | Symbol   | Minimum | Typical | Maximum | Unit | Condition            |

|---------------------------------|------------------|----------|---------|---------|---------|------|----------------------|

| Parameter                       | Direction        | Symbol   | Min     | Тур     | Max     | Unit | Condition            |

| Regulator input Voltage         | I                | VBAT-DIG | 1.8     | 3.3     | 3.47    | V    |                      |

| Analog Voltage                  | I                | VBAT-ANA | 1.8     | 3.3     | 3.47    | V    |                      |

| Non-regulated Analog<br>Voltage | l <sup>(1)</sup> | AVDD     | 0.95    | 1.0     | 1.05    | V    | LDO_ANA shut<br>down |

| IO Voltage                      | I                | VBAT-IO  | 1.8     | 3.3     | 3.47    | V    |                      |

| LED Driver Voltage              | I                | VBAT-LED | 1.8     | 3.3     | 3.47    | V    |                      |

| Non-regulated Core<br>Voltage   | l <sup>(1)</sup> | VDD      | 0.76    | 0.8     | 0.84    | V    | LDO_DIG shut<br>down |

Table 3.

DC Characteristics and Operating Conditions (1 of 2)

| Parameter                                | Direction | Symbol          | Minimum | Typical | Maximum | Unit | Condition                |

|------------------------------------------|-----------|-----------------|---------|---------|---------|------|--------------------------|

| Non-regulated RAM<br>Voltage             | (1)       | VRR             | 0.76    | 0.8     | 0.84    | V    | RET_LDO_DIG<br>shut down |

| Sensor IO Voltage                        | I         | VDDO2           | 1.8     | 3.3     | 3.47    | V    |                          |

| Host IO Voltage                          | 0         | VDDO1           | 1.8     | 3.3     | 3.47    | V    |                          |

| Input voltage HIGH                       |           | V <sub>IH</sub> | 2.0     |         |         | V    |                          |

| Input voltage LOW                        |           | V <sub>IL</sub> |         |         | 0.8     | V    |                          |

| Output voltage HIGH                      |           | V <sub>OH</sub> | 2.4     |         |         | V    |                          |

| Output voltage LOW                       |           | V <sub>OL</sub> |         |         | 0.4     | V    |                          |

| Operating Power<br>(PD=1, PD_RAM=1)      |           |                 |         | 12      |         | mA   | Vbat = 3.3 V             |

| Retention Mode Power<br>(PD=0, PD_RAM=1) |           |                 |         | 2-3     |         | mA   | Vbat = 3.3 V             |

| Sleep Power<br>(PD=0, PD_RAM=0)          |           |                 |         | 10      |         | nA   | Vbat = 3.3 V             |

| Operating Temperature                    |           | T <sub>A</sub>  | -10     |         | +85     | °C   |                          |

| Junction Temperature                     |           | TJ              | 1       |         | +100    | °C   |                          |

| Table 3. | DC Characteristics and Operating Conditions | (2 of 2) |

|----------|---------------------------------------------|----------|

|----------|---------------------------------------------|----------|

(1) These are typically regulated outputs of the device but internal regulators can be disabled and voltage source can optionally be fed externally.

#### **Analog Characteristics** 3.3

#### Table 4. Analog Characteristics

| Parameter                                                                         | Symbol   | Maximum            | Unit |  |

|-----------------------------------------------------------------------------------|----------|--------------------|------|--|

| Parameter                                                                         | Symbol   | Max                | Unit |  |

| Microphone Input                                                                  | MIC_IN   | 1.0                | Vp-р |  |

| Analog Photocell Input                                                            | PCELL_IN | 1.0                | V    |  |

| LED Output                                                                        | LED_OUT  | VBAT_LED           | V    |  |

| LED Feedback                                                                      | LED_FB   | 1.8 <sup>(1)</sup> | V    |  |

| <i>FOOTNOTES:</i> <sup>(1)</sup> With high gain mode enabled. Typical range is 0- | 1.0 V.   |                    | ·    |  |

# B3.4Timing Specifications

#### Table 5.Timing Specifications (1 of 2)

| Pin Name | I/O | Interface Name {dir}                 | Input Setup (ns) | Input Hold (ns) | Clock-to-Output (ns) | Clock             | Clock Period ([ns)    |

|----------|-----|--------------------------------------|------------------|-----------------|----------------------|-------------------|-----------------------|

|          |     | 1                                    | L                | GPIO            |                      |                   |                       |

| GPIO[4]  | 10  | gpio4 [IO] / I_SCL2 [I] / O_SCL2 [O] | 50 / 15 / NA     | 3/3/NA          | 54 / NA / 15         | XTI/2 / XTI / XTI | 74.07 / 37.07 / 37.07 |

| GPIO[3]  | 10  | gpio3 [IO] / I_SDA2 [I] / O_SDA2 [O] | 50 / 15          | 3/3/NA          | 54 / NA / 15         | XTI/2 / XTI / XTI | 74.07 / 37.07 / 37.07 |

| GPIO[2]  | 10  | gpio2 [IO]                           | 50               | 3               | 54                   | XTI/2             | 74.07                 |

| GPIO[1]  | 10  | gpio1 [IO]                           | 50               | 3               | 54                   | XTI/2             | 74.07                 |

| GPIO[0]  | 10  | gpio0 [IO]                           | 50               | 3               | 54                   | XTI/2             | 74.07                 |

|          |     | 1                                    | Sen              | sor Interface   |                      |                   |                       |

| SDATA[7] | 10  | sdata7 [l]                           | 23               | 3               |                      | spclk             | 37.037                |

| SDATA[6] | 10  | sdata6 [l]                           | 23               | 3               |                      | spclk             | 37.037                |

| SDATA[5] | 10  | sdata5 [l]                           | 23               | 3               |                      | spclk             | 37.037                |

| SDATA[4] | 10  | sdata4 [l]                           | 23               | 3               |                      | spclk             | 37.037                |

| SDATA[3] | 10  | sdata3 [l]                           | 23               | 3               |                      | spclk             | 37.037                |

| SDATA[2] | 10  | sdata2 [l]                           | 23               | 3               |                      | spclk             | 37.037                |

| SDATA[1] | 10  | sdata1 [l]                           | 23               | 3               |                      | spclk             | 37.037                |

| SDATA[0] | 10  | sdata0 [l]                           | 23               | 3               |                      | spclk             | 37.037                |

| SVREF    | 10  | svref [I] / gpio5 [IO]               | 23 / 50          | 3/3             | 54                   | spclk / XTI/2     | 37.037 / 74.07        |

| SHREF    | 10  | shref [I] / gpio6 [IO]               | 23 / 50          | 3/3             | 54                   | spclk / XTI/2     | 37.037 /74.07         |

| SPCLK    | 1   | spclk [l]                            |                  |                 |                      |                   |                       |

#### Table 5. Timing Specifications (2 of 2)

| Pin Name | I/O | Interface Name {dir}                             | Input Setup (ns)  | Input Hold (ns)    | Clock-to-Output (ns) | Clock                            | Clock Period ([ns)                |

|----------|-----|--------------------------------------------------|-------------------|--------------------|----------------------|----------------------------------|-----------------------------------|

|          |     |                                                  | Sensor Int        | erface (continued) | •                    |                                  |                                   |

| SCLK     | 0   | sclk [O]                                         |                   |                    |                      |                                  |                                   |

| S_SCL    | 10  | s_scl [IO]                                       | 23                |                    | 24                   | XTI                              | 37.037                            |

| S_SDA    | 10  | s_sda [IO]                                       | 23                |                    | 24                   | XTI                              | 37.037                            |

| S_GP     | 10  | sccb_e [O] / gpio7 [IO]                          | NA / 47           | NA / 3             | 24 / 54              | XTI / hstclk [I] XTI/2<br>[O]    | 37.037 / 74.07                    |

|          |     | 1                                                | Но                | st Interface       |                      |                                  |                                   |

| HSCLK    | 10  | hsclk [I] / scl [I] / txd [O]                    | NA / 60 / NA      | NA / 3 / NA        | NA / NA / 54         | NA / XTI/2 / XTI/2               | NA / 74.07 / 74.07                |

| HSIMO    | 10  | hsimo [I] / rts [O]                              | 26 / NA           | 3 / NA             | NA / 52              | hsclk_inv / XTI/2                | 37.037 / 74/07                    |

| HSOMI    | 10  | spi_out [O] / sda_out [O] / sda_in [I] / cts [I] | NA / NA / 50 / 50 | NA / NA / 3 / 3    | 10 / 52 / NA / NA    | hsclk / XTI/2 / XTI/2<br>/ XTI/2 | 37.037 / 74.07 / 74.07 /<br>74.07 |

| HSS      | I   | hss(auto-detect) [I] / hss (SPI) [I] / rxd [I]   | 50 / 25 / 50      | 3/3/3              |                      | XTI/2 / hsclk / XTI/2            | 74.07 / 37.037 / 74.07            |

26

CX93510 Data Sheet

# **Sensor Interface**

# 4.1 Supported Resolutions and Frame/Data Rates

### 4.1.1 Requirements

| Input resoluti         | ons | Max 640x480 (VGA), Min 320x240 (QVGA) or any subset<br>in between with multiple 16x16, so 512x256, 352x240<br>(CIF) etc., are acceptable. If the scaler is enabled, subsets<br>in between the minimum and maximum frame sizes must<br>be multiples of 32x32, therefore limiting the minimum input<br>resolution to 320x256. |  |  |  |  |

|------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Sensor I/F: 8-bit data |     | Uses 656-compatible embedded SAV/EAV timing codes or separate horizontal and vertical signaling.                                                                                                                                                                                                                            |  |  |  |  |

| Input pixel clock rate |     | Up to 27 MHz; internal clock rate: 27 MHz                                                                                                                                                                                                                                                                                   |  |  |  |  |

| NOTE                   |     |                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

*NOTE:* The input pixel clock rate must be less than the internal clock rate.

The interface will support cropping of the incoming image so that sensors of other resolutions can be supported. However, internal buffer sizes will constrain the resulting image size to 640x480 or smaller.

# 4.2 Supported Data Formats

The following input data formats are supported:

### 4.2.1 YCbCr 4:2:2

Configuration registers will allow swapping of Cr and Cb and/or luminance and chrominance values. Scanning must be in progressive (non-interlaced) mode.

### 4.2.2 Monochrome (Y Only)

To support monochrome mode, the image sensor interface can be configured to receive only Y values (8bpp). Registers will also allow the design to receive and ignore Cr and Cb values. In either of these monochrome modes, the sensor interface will output only Y (luminance) data.

## 4.3 Continuous vs. Limited Frame Mode

Configuration registers allow the sensor to capture frames continuously, or capture a limited group of frames (up to 63) and then stop. In Limited Frame mode, the FRAME\_NUM register field indicates how many frames to capture before stopping. In continuous mode, the sensor continues to capture frames indefinitely.

In either mode, the FRAME\_SKIP register field is used to indicate how many frames to skip between captured frames. For example, if this value is set to 0x02, then every third frame is captured. This allows the user to capture data at 10 fps if the sensor is running at 30 fps.

# 4.4 Sensor Interface Timing

The sensor interface operates in one of two modes. The first mode uses the SHREF and SVREF inputs to determine the timing of image data. The second mode uses packets embedded in the data stream to determine the timing.

**NOTE:** The CX93510 must see at least three rising edges of SPCLK before it is able to detect the first SVREF edge and capture the first frame.

### 4.4.1 Discrete Timing Mode

This mode of operation uses the SHREF, SVREF, and SPCLK inputs to determine timing of image data. The SPCLK (pixel clock) input can be up to 27 MHz. The following diagram illustrates how the settings in the H\_ACT, H\_CAP\_DLY and H\_CAP\_WIDTH registers relate to the capture of data on the SDATA bus:

Figure 7. Discrete Timing Mode

The H\_POL register bit will internally invert the SHREF input, allowing the timing to be measured relative to the falling edge of SHREF instead of the rising edge. Data and SHREF are clocked in on the rising edge of SPCLK. Note that the value in the H\_ACT register is measured in SCLKs. Values in the H\_CAP\_DLY and H\_CAP\_WIDTH registers are in multiples of 8 pixels.

The vertical timing is similar, except that V\_ACT, V\_CAP\_DLY and V\_CAP\_HEIGHT values are compared to a count of the active-going edges of SHREF instead of rising SCLKs. The value in the V\_ACT register is used to count lines between the active edge of SVREF and the start of image data. V\_CAP\_DLY counts multiples of 8 lines from the start of image data to the start of capture, and V\_CAP\_HEIGHT \* 8 indicates how many lines are captured in each frame.

# 4.5 Embedded Timing Mode

These embedded packets are similar to those used in the ITU-BT656 standard. The H\_ACT, H\_CAP\_DLY, H\_CAP\_WIDTH, V\_ACT, V\_CAP\_DLY, and V\_CAP\_WIDTH registers operate as they do in discrete timing mode, with the following differences:

- The H\_ACT count begins upon receipt of an SAV code with the H bit cleared after previously receiving an EAV code with the H bit set.

- The V\_ACT count begins upon receipt of an SAV code with the V bit cleared after previously receiving an SAV code with the V bit set.

- The vertical counters count SAV packets.

- Receipt of an EAV packet will terminate a line even if the H\_CAP\_WIDTH count has not been reached. If the H\_CAP\_WIDTH count has not been reached, image capture will stop, and the EMBD\_CDE\_ERR register bit will be set.

- Receipt of an SAV or EAV packet with the V bit set will terminate a frame even if the V\_CAP\_HEIGHT count has not been reached. If the V\_CAP\_HEIGHT count has not been reached, image capture will stop, and the EMBD\_CDE\_ERR register bit will be set.

Figure 8 depicts a typical scenario, in which video data is being captured from a window within the active region. Note that in most likely scenarios, H\_CAP\_DLY will be set to 0, (indicating that data capture will begin immediately after the SAV code), and H\_CAP\_WIDTH will be set such that the end of capture occurs just before the EAV code.

#### Figure 8. Typical Video Data Capture

The SAV and EAV packets are four bytes long, with the first three bytes being FF, 00, 00. The fourth byte includes the V bit in bit 5, and the H bit in bit 4. All other bits in the fourth byte (including protection bits) are ignored.

#### Table 6. SAV and EAV Packets

| Condition      | 656-Compatible Code |

|----------------|---------------------|

| Start of frame | 8'bXX00XXXX         |

| End of Frame   | 8'bXX1XXXXX         |

| Start of Line  | 8'bXX00XXXX         |

| End of Line    | 8'bXXX1XXXX         |

## 4.6 Sensor Clock

The CX93510 provides a 27 MHz clock output (SCLK) to be used as the clock input to the attached image sensor.

Some sensors will use an internal PLL to produce a slower clock for the pixel data interface, SPCLK must be < 27 MHz.

Some sensors include modes in which SPCLK is gated during blanking regions. Some sensors also gate SPCLK if the sensor is scaling the image (which results in a delay between pixels). Because of this behavior, the only logic that can use SPCLK is the logic which interfaces directly with the sensor. The data capture must be synchronized to an internal clock before any data pipeline. Some sensors can also stop SPCLK between lines and/or frames. For this reason, all logic that uses SPCLK must be in a state to accept the start of a new line on the SPCLK edge following the end of the current line. Similarly, the logic must be able to react to the start of a new frame on the SPCLK edge following the end of the current frame. When embedded codes are used for timing, it is assumed that the clock will operate while the codes are sent on the bus.

## 4.7 LED Control

The sensor interface module can be configured to trigger the LED to turn on and off relative to the end of frame. When this feature is enabled, the LED will be turned off when the last pixel of the image is captured, and the LED will be turned on again after a configurable delay. If en\_lfc is used, the LED will remain off after the last frame is captured.

If the frame\_skip feature is enabled, the LED will not be toggled at the end of a skipped frame. The LED\_ON\_DELAY should be programmed to a large enough value to keep the LED off until the start of the next non-skipped frame.

## 4.8 Sensor Control Interface

An attached image sensor is controlled using an I2C or SCCB interface. Depending on the specifics of the connected sensor, this interface allows for programming of image size, flash, shutter, auto-focus, brightness, contrast, white balance, color correction, and other settings.

The interface includes a FIFO for posting write transactions to the sensor. The FIFO is capable of storing an 8- or 16-bit address and an or 16-bit data value in each entry, and can contain up to 4 entries. The host can add a transaction by writing to the I2C\_ADDR and I2C\_DATA registers, and the number of entries currently in the FIFO can be determined by reading the I2C\_CFG\_FIFO\_CNT register field. The count in this register will decrement upon completion of the write transaction on the I2C/SCCB bus, and will increment with writes to the I2C\_DATA registers. See the register description for more details.

The interface is configured to I2C by default. If SCCB is to be used, the sensor will have to be reset after configuring the interface to SCCB.

The interface allows the host to enqueue up to 4 write transactions by repeatedly writing to the address and write-data registers. Read transactions cannot be pipelined in this manner. The address for write entries can be auto-incremented.

# 4.8.1 I<sup>2</sup>C

A master  $I^2C$  or Serial Camera Control Bus (SCCB) interface is necessary to configure and operate the sensor. This allows a system master to use this interface to program a sensor with an  $I^2C$  or SCCB interface even if the system master does not interface to  $I^2C$  or SCCB.

The  $I^2C$  interface supports sub-address sizes of 0, 1, or 2 bytes. (A sub address size of 0 bytes will produce no sub-address phase during the  $I^2C$  transaction.) The interface also supports data sizes of 1 or 2 bytes per transaction.

The I<sup>2</sup>C master interface can be routed to the S\_SCL and S\_SDA pins, which are on the sensor's power domain, or to the GPIO[4:3] pins, which are on the host's power domain. Configuration registers allow the host to switch between these two sets of pins between I<sup>2</sup>C transactions, as long as the S\_SCL and S\_SDA pins are being used for I<sup>2</sup>C and not SCCB. (in which case only the GPIO[4:3] pins can be used for I<sup>2</sup>C transactions.)

A data bit rate of 100/400 kHz is supported.

### 4.8.2 SCCB

The SCCB control bus consists of four signals, as listed in Table 7:

| Signal Name | I/O (Relative to CX93510) | Description                                                                                                                                      |

|-------------|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| SCCB_E      | Output                    | Chip Select Output; Drive to 0 to initiate transaction or when in suspend mode                                                                   |

| SIO_C       | Output                    | Clock signal; similar to I <sup>2</sup> C clock                                                                                                  |

| SIO_D       | Input/Output              | Data signal; similar to I <sup>2</sup> C data                                                                                                    |

| PWDN        | Output                    | Power Down – implemented using GPIO. A configuration bit is used to transition the above signals between operational mode and SCCB suspend mode. |

#### Table 7. SCCB Signals

Although the SCCB SIO\_C and SIO\_C signals are similar to I2C signals, there are some slight differences in the protocol. Details can be found in the SCCB Specification. SCCB\_E is not used on all sensors. This functionality can be disabled, which allows this pin to be used as a GPIO[7].

## 4.9 Miscellaneous Interface Controls

In addition to the data interface and the control interface, some image sensor chips require additional inputs (CX93510 outputs) that can be implemented using GPIO pins. These signals include: Reset, Power Down, and Standby.

In order to initiate a suspend condition on the SCCB bus, the GPIO that is used for the PWDN signal is manipulated separately from the SCCB\_SUSPEND configuration bit. Software must drive the PWDN signal active, and then set the PWDN\_MODE configuration bit to cause the SCCB interface logic to drive the other SCCB signals low. To end the suspend condition, software must clear the PWDN\_MODE bit and then deactivate the PWDN signal.

### 4.10 Usage Scenarios

This section highlights the requirement for the external uP to stay involved in managing the sensor during capture and in between captured frames to optimize power usage.

### 4.10.1 Limited/Single Frame Mode

One likely usage scenario is for the host to capture multiple frames at regular intervals. To do this, host firmware will need to follow these steps:

- 1. Apply Power/Reset to the CX93510 and the CMOS image sensor.

- 2. Configure the I2C/SCCB interface to allow communication with the image sensor.

- 3. Configure the image sensor via the I2C/SCCB interface.

- 4. Configure the CX93510 to receive and process the frame.

- 5. Initiate capture of a single frame using limited frame mode.

- 6. Initiate capture of the frame in the image sensor. Depending on the sensor and the hardware configuration, this may require manipulation of a CX93510 GPIO to trigger the picture, or it could require writing to a configuration register in the sensor.

- 7. Poll the sensor interface configuration register or the frame buffer status register to determine when capture has completed.

- 8. If necessary, turn off the image sensor.

- 9. Process the resulting data.

- **10.** After the appropriate amount of time has passed (e.g. 100 ms for 10fps capture), repeat steps 5-9.

Some image sensors can be configured to take a single frame, so step 8 may be unnecessary.

### 4.10.2 Continuous Frame Mode

Some sensors can also be configured to capture images periodically (i.e. "movie mode"). In this case, a streamlined programming sequence can be followed:

- 1. Apply Power/Reset to the CX93510 and the CMOS image sensor.

- 2. Configure the I2C/SCCB interface to allow communication with the image sensor.

- 3. Configure the image sensor via the I2C/SCCB interface.

- 4. Configure the CX93510 to receive and process the frames.

- 5. Initiate capture using continuous frame mode.

- 6. Initiate capture of frames in the image sensor.

- 7. Poll the sensor frame buffer status register to determine when capture and compression of frames has completed, and process frames as they are received.

- 8. Once the required number of frames has been received, the host can shut off the image sensor and turn off the continuous frame mode bit.

# 5.1 Format and Scaling

All video data is input, maintained, and output as 8-b (per component) YCbCr 4:2:2, 8b Y only for black and white case. Half H and V scaling rate is supported as well as pass through (bypass). The output can range from VGA to a minimum size of 160x128. When using the scaler, the input must be a 32x32 multiple. Typically, this scaler is for re-sizing VGA down to QVGA.

# 5.2 Bandwidth and Storage Requirements

The Sensor I/F is used as the interface mechanism to transport images (video) into the CX93510 device. The input rate is a function of the sensor resolution (H,V), sensor delivery of data (fps and i/f rate), and the format (b/p).

The video stream output consists of MJPEG where each frame is compressed as an independent still image using the JPEG standard or MJPEG-DPCM (differential mode). The video bandwidth & storage requirements depend on the input, processing, and output.

### 5.2.1 Storage of Compressed Images

In the PIR Sensor application, images are input & compressed at the rate of up to 10 fps. The images are buffered in an integrated 256 KB/128 KB image frame buffer that can retain the captured compressed images while the rest of the SoC is put to sleep.

The number of images that can be accumulated in the frame buffer is dependant on the JPEG compression obtained. Note that the compression ratio is not a selectable option on the device itself. The compression obtained is highly dependant on the image being captured. Color and image detail can greatly influence the amount of compression achieved. In the case of differential JPEG mode, the amount of motion will also cause the file sizes of the difference frames to vary widely. Table 8 illustrates the number of possible images stored based on arbitrary compression ratios and are shown as an example only.

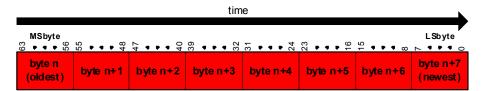

|        |     | VGA    |       |        |      | QVGA   |       |        |  |