## **Advanced Battery Management PMIC With** Ultralow I<sub>Q</sub> Buck and Buck Boost

**ADP5360** Data Sheet

#### **FEATURES**

Linear battery charger

High accuracy and programmable charge terminal voltage and charge current up to 320 mA

Compliant with JEITA charge temperature specification

Li-lon and Li-Poly battery monitor and protection Voltage-based fuel gauge with adaptive filter limitation Independent battery protection of overcharge and overdischarge

Temperature sensor with external NTC Ultralow quiescent current buck converter Quick output discharge option Ultralow quiescent current buck boost converter Quick output discharge option Supervisory with MR and watchdog timer Shipment mode extends battery life Full I<sup>2</sup>C programmability with dedicated interrupt pin

#### **APPLICATIONS**

Rechargeable Li-Ion/Li-Poly battery-powered devices Portable consumer devices Portable medical devices Wearable devices

Trademarks and registered trademarks are the property of their respective owners.

#### **GENERAL DESCRIPTION**

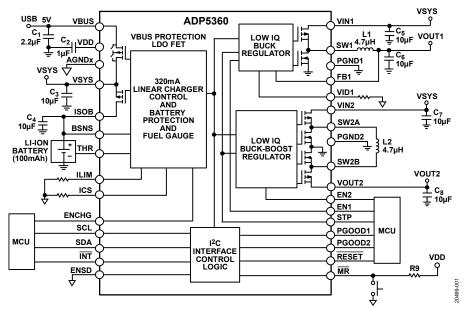

The ADP5360 combines one high performance linear charger for a single lithium-ion/lithium-polymer (Li-Ion/Li-Poly) battery with a programmable, ultralow quiescent current fuel gauge and battery protection circuit, one ultralow quiescent buck, one buck boost switching regulator, and a supervisory circuit that can monitor output voltage.

The ADP5360 charger operates at up to 6.8 V. This prevents USB bus spiking during disconnect or connect scenarios.

The ADP5360 features an internal isolation field effect transistor (FET) between the linear charger output and the battery node. The full battery protection features are activated when the device is in the battery overcharge and overdischarge fault conditions.

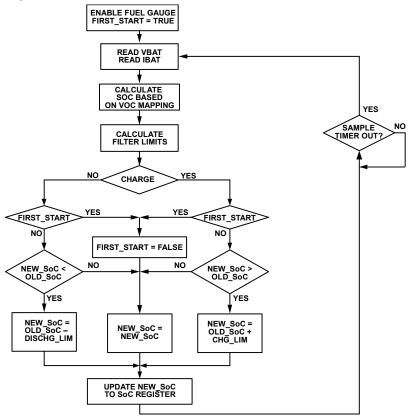

The ADP5360 fuel gauge uses a voltage-based algorithm with an adaptive filter limitation solution. The fuel gauge reports real time battery state of charge for the rechargeable Li-Ion battery with ultralow quiescent current.

The ADP5360 buck regulator operates at 1 MHz switching frequency in forced pulse-width modulation (FPWM) mode. In hysteresis mode, the regulator achieves excellent efficiency at a low output power.

The ADP5360 buck boost regulator only operates in hysteresis mode and outputs a voltage less than or greater than battery voltage.

The ADP5360 supervisory circuits monitor the regulator output voltage and provide a power-on reset signal to the system. A watchdog timer and an external push-button can reset the microprocessor.

The I<sup>2</sup>C-compatible interface enables the programmability of all battery charging parameters, protection threshold, buck output voltage, and status bit readback.

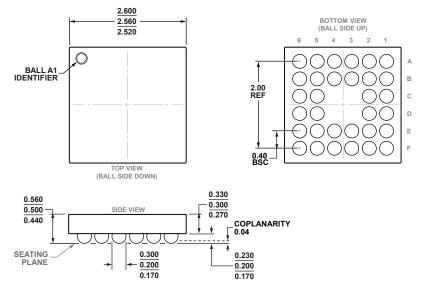

The ADP5360 operates over the -40°C to +85°C junction temperature range and is available in 32-ball, 2.56 mm  $\times$  2.56 mm wafer level chip scale package (WLCSP).

## **TABLE OF CONTENTS**

| Features                                                    | 1‡  |

|-------------------------------------------------------------|-----|

| Applications                                                | 1#  |

| General Description                                         | 1#  |

| Revision History                                            | 2#  |

| Functional Block Diagram                                    | 3‡  |

| Specifications                                              | 4‡  |

| Battery Charger Specifications                              | 4#  |

| Battery Monitor Specifications                              | 6#  |

| Buck Regulator Specifications                               | 6‡  |

| Buck Boost Regulator Specifications                         | 7‡  |

| I <sup>2</sup> C-Compatible Interface Timing Specifications | 7‡  |

| Recommended Input and Output Capacitance and Inductance     | 8#  |

| Absolute Maximum Ratings                                    | 9#  |

| Thermal Resistance                                          | 9#  |

| ESD Caution                                                 | 9#  |

| Pin Configuration and Function Descriptions                 | 10# |

| Typical Performance Characteristics                         | 12# |

| Typical Waveforms                                           | 16# |

| Theory of Operation                                         | 20# |

| Battery Charger                                             | 20# |

| Battery Isolation FET                                       | 22‡ |

| Battery Detection                                           | 22‡ |

| Battery Temperature                                         | 23# |

| Battery Fuel Gauge                                          | 25# |

| Battery Protection                             | 8# |

|------------------------------------------------|----|

| Buck Regulator Operation2                      | 8# |

| Buck Boost Regulator Operation                 | 0# |

| Supervisory                                    | 1# |

| Shipment Mode                                  | 2# |

| Fault Recovery                                 | 2# |

| Thermal Management                             | 2# |

| I <sup>2</sup> C Interface                     | 3# |

| I <sup>2</sup> C Addresses                     | 3# |

| SDA and SCL Pins                               | 3# |

| Interrupts3                                    | 3# |

| Control Register Map3                          | 5# |

| Fuel Gauge: Register Bit Descriptions4         | 5# |

| Switching Regulator: Register Bit Descriptions | 8# |

| Supervisory: Register Bit Descriptions         | 9# |

| Status and Fault: Register Bit Descriptions50  | 0# |

| Applications Information                       | 3# |

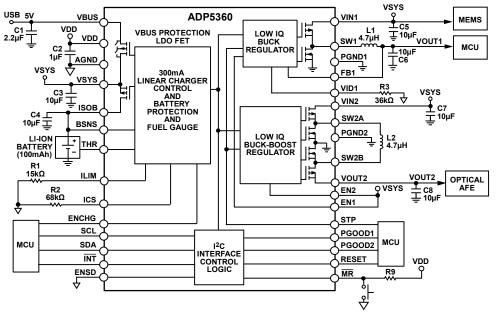

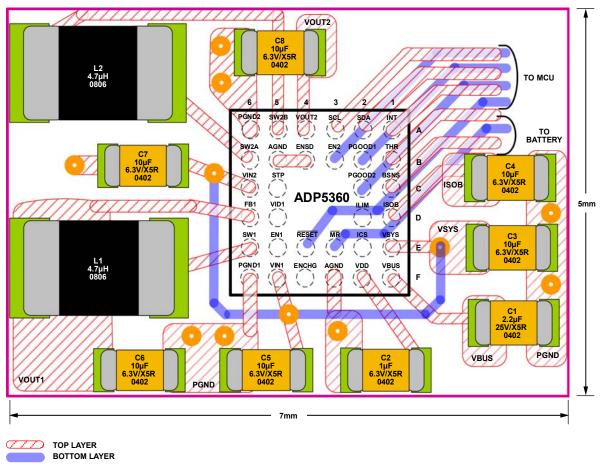

| Typical Application Circuit                    | 3# |

| External Components54                          | 4# |

| PCB Layout Guidelines                          | 6# |

| Typical Application Circuit in Healthcare5     | 3# |

| Factory-Programmable Options5                  | 7# |

| Outline Dimensions                             | 9# |

| Ordering Guide5                                | 9# |

## **REVISION HISTORY**

10/2019—Revision 0: Initial Version

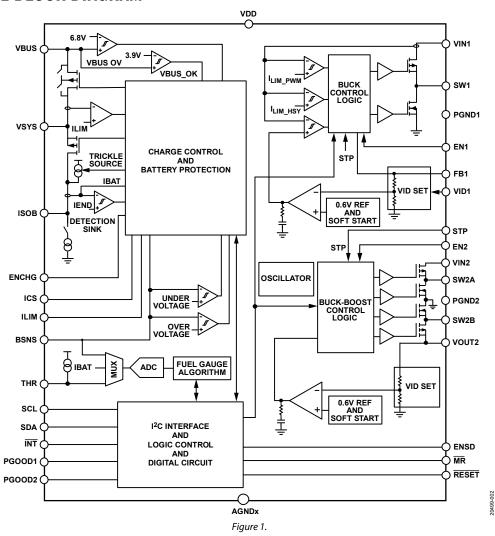

## **FUNCTIONAL BLOCK DIAGRAM**

## **SPECIFICATIONS**

## **BATTERY CHARGER SPECIFICATIONS**

-40 °C < junction temperature ( $T_J$ ) < +85 °C, voltage of the VBUS pin ( $V_{VBUS}$ ) = 5.0 V, voltage of the ISOB pin ( $V_{ISOB}$ ) = 3.8 V,  $C_1$  = 2.2  $\mu$ F,  $C_2$  = 1  $\mu$ F,  $C_3$  =  $C_4$  = 10  $\mu$ F (see Figure 60), all registers are at default values, unless otherwise noted.

Table 1.

| Parameter                                          | Symbol                        | Test Conditions/Comments                                                                         | Min  | Тур                       | Max  | Unit |

|----------------------------------------------------|-------------------------------|--------------------------------------------------------------------------------------------------|------|---------------------------|------|------|

| GENERAL PARAMETERS                                 |                               |                                                                                                  |      |                           |      |      |

| Undervoltage Lockout (UVLO)                        | V <sub>UVLO</sub>             | Rising threshold, voltage of the ISOB pin, $V_{VBUS} = 0$                                        |      | 2.1                       | 2.15 | V    |

|                                                    |                               | Falling threshold, voltage of the ISOB pin, $V_{VBUS} = 0$                                       | 1.8  | 1.88                      |      | V    |

| Input Current Limit                                | ILIM                          | I <sub>LIM</sub> = 100 mA                                                                        |      | 95                        | 100  | mA   |

| Operation Current                                  |                               |                                                                                                  |      |                           |      |      |

| VBUS Consumption                                   | I <sub>Q_BUS</sub>            | All enabled, no charge current                                                                   |      | 1.5                       | 2    | mA   |

| Battery Consumption                                | $I_{Q\_PRO}$                  | Only enable battery protection, $V_{VBUS} = 0$                                                   |      | 0.25                      | 1.8  | μΑ   |

|                                                    | I <sub>Q_FG_ACT</sub>         | Fuel gauge, active mode, $V_{VBUS} = 0$                                                          |      | 3.5                       | 5    | μΑ   |

|                                                    | I <sub>Q_FG_SLEEP</sub>       | Fuel gauge, sleep mode, V <sub>VBUS</sub> = 0                                                    |      | 0.2                       | 0.85 |      |

|                                                    | $I_{Q\_REG}$                  | Enable buck and buck boost, V <sub>VBUS</sub> = 0                                                |      | 0.34                      | 1    | μΑ   |

|                                                    | I <sub>Q_DISALL</sub>         | All disabled, V <sub>VBUS</sub> = 0                                                              |      | 150                       | 450  | nA   |

|                                                    | $I_{Q\_SHIP}$                 | Shipment mode, T <sub>J</sub> = 25°C                                                             |      | 10                        | 50   | nA   |

|                                                    |                               | Shipment mode, $T_J = -40^{\circ}\text{C}$ to $+85^{\circ}\text{C}$                              |      |                           | 310  | nA   |

| CHARGING PARAMETERS                                |                               |                                                                                                  |      |                           |      |      |

| Fast Charge Constant Current (CC) Mode             | I <sub>CHG</sub>              | $I_{CHG} = 100 \text{ mA}$                                                                       | 94   | 100                       | 106  | mA   |

| Fast Charge Current Accuracy                       |                               | $I_{CHG} = 10 \text{ mA to } 320 \text{ mA}, T_J = 0^{\circ}\text{C to } 85^{\circ}\text{C}^{1}$ | -15  |                           | +15  | %    |

| Trickle Charge Current <sup>1</sup>                | I <sub>TRK_DEAD</sub>         | $I_{TRK_DEAD} = 5 \text{ mA, T}_J = 0^{\circ}\text{C to } 85^{\circ}\text{C}^{1}$                | 4    | 5                         | 6    | mA   |

| Weak Charge Current                                | I <sub>CHG_WEAK</sub>         |                                                                                                  |      | $I_{TRK\_DEAD} + I_{CHG}$ |      | mA   |

| Trickle to Weak Charge Threshold <sup>1</sup>      | $V_{TRK\_DEAD}$               | $V_{TRK\_DEAD} = 2.5 \text{ V}$                                                                  | 2.41 | 2.5                       | 2.57 | ٧    |

| Trickle to Weak Charge Threshold<br>Hysteresis     | $\Delta V_{\text{TRK\_DEAD}}$ |                                                                                                  |      | 100                       |      | mV   |

| Weak to Fast Charge Threshold <sup>1</sup>         | $V_{WEAK}$                    | $V_{WEAK} = 3.0 \text{ V}$                                                                       | 2.88 | 3.0                       | 3.08 | V    |

| Weak to Fast Charge Threshold Hysteresis           | $\Delta V_{\text{WEAK}}$      |                                                                                                  |      | 100                       |      | mV   |

| Battery Termination Voltage                        | $V_{TRM}$                     |                                                                                                  |      |                           |      | V    |

| Termination Voltage Accuracy                       |                               | $V_{TRM} = 4.2 \text{ V}$ on the BSNS pin, $T_J = 25^{\circ}\text{C}$                            | 4.18 | 4.200                     | 4.22 | V    |

|                                                    |                               | $V_{TRM} = 4.2 \text{ V}$ , on the BSNS pin, $T_J = 0^{\circ}\text{C}$ to $85^{\circ}\text{C}^1$ | -1   |                           | +1   | %    |

| Charge Complete Current <sup>1</sup>               | I <sub>END</sub>              | $I_{END} = 5 \text{ mA}, T_J = 0^{\circ}\text{C to } 85^{\circ}\text{C}^{1}$                     | 2    | 5                         | 8    | mA   |

| Recharge Voltage Differential <sup>1</sup>         | $V_{RCH}$                     |                                                                                                  |      | 120                       |      | mV   |

| BATTERY ISOLATION FET                              |                               |                                                                                                  |      |                           |      |      |

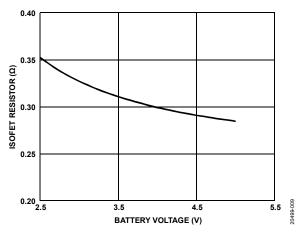

| Resistance Between ISOB and VSYS                   | R <sub>DSON_ISO</sub>         | V <sub>VBUS</sub> = 0 V, current of the ISOB pin (I <sub>ISOB</sub> ) = 100 mA                   |      | 145                       | 220  | mΩ   |

| LOW DROPOUT (LDO) AND HIGH VOLTAGE<br>BLOCKING FET |                               |                                                                                                  |      |                           |      |      |

| Regulated System Voltage <sup>1</sup>              | V <sub>SYS_REG</sub>          | $V_{TRM} = 4.2 \text{ V, VSYSTEM} = V_{TRM} + 200 \text{ mV}$                                    |      | 4.4                       |      | ٧    |

| High Voltage Blocking FET On<br>Resistance         | R <sub>DSON_HV</sub>          | I <sub>VBUS</sub> = 100 mA                                                                       |      | 550                       | 820  | mΩ   |

| Input Voltage                                      |                               |                                                                                                  |      |                           |      |      |

| Good Threshold                                     | V <sub>VBUS_OK</sub>          |                                                                                                  |      |                           |      |      |

| Rising                                             | V <sub>VBUS_OK_RISE</sub>     |                                                                                                  |      | 3.9                       | 4.0  | ٧    |

| Falling                                            | V <sub>VBUS_OK_FALL</sub>     |                                                                                                  | 3.5  | 3.6                       |      | ٧    |

| Overvoltage Threshold                              | $V_{VBUS\_OV}$                |                                                                                                  |      |                           |      |      |

| Rising                                             | V <sub>VBUS_OV_RISE</sub>     |                                                                                                  |      | 6.8                       | 7.0  | ٧    |

| Falling                                            | $V_{VBUS\_OV\_FALL}$          |                                                                                                  | 6.4  | 6.6                       |      | V    |

| Parameter                                 | Symbol                  | Test Conditions/Comments                                                                                                                 | Min  | Тур  | Max  | Unit |

|-------------------------------------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| THERMAL PROTECTION                        |                         |                                                                                                                                          |      |      |      |      |

| Thermal Shutdown Temperature <sup>2</sup> | T <sub>SD</sub>         | T <sub>J</sub> rising                                                                                                                    |      | 110  |      | °C   |

|                                           |                         | TJ FALLING                                                                                                                               |      | 100  |      | °C   |

| THERMISTOR CONTROL                        |                         |                                                                                                                                          |      |      |      |      |

| Thermistor Current                        |                         |                                                                                                                                          |      |      |      |      |

| $R_{NTC} = 10 \text{ k}\Omega$            | I <sub>NTC_10k</sub>    |                                                                                                                                          | 57.5 | 60   | 62   | μΑ   |

| $R_{NTC} = 47 \text{ k}\Omega$            | I <sub>NTC_47k</sub>    |                                                                                                                                          | 11.5 | 12   | 12.5 | μΑ   |

| $R_{NTC} = 100 \text{ k}\Omega$           | I <sub>NTC_100k</sub>   |                                                                                                                                          | 5.65 | 6    | 6.35 | μΑ   |

| BATTERY DETECTION                         |                         |                                                                                                                                          |      |      |      |      |

| Sink Current                              | Isink                   |                                                                                                                                          | 4.1  | 6    | 7    | mA   |

| Source Current                            | I <sub>SOURCE</sub>     | $I_{SOURCE} = I_{TRK\_DEAD}$                                                                                                             | 2    | 2.5  | 3    | mA   |

| Battery Threshold                         |                         |                                                                                                                                          |      |      |      |      |

| Low                                       | $V_{BATL}$              |                                                                                                                                          | 1.92 | 2    | 2.06 | V    |

| High                                      | $V_{BATH}$              |                                                                                                                                          | 3.27 | 3.4  | 3.48 | ٧    |

| Battery Detection Timer                   | <b>t</b> batok          |                                                                                                                                          |      | 333  |      | ms   |

| TIMERS                                    |                         |                                                                                                                                          |      |      |      |      |

| Start Charging Delay Timer                | t <sub>START</sub>      |                                                                                                                                          |      | 300  |      | ms   |

| Trickle Charge Timer <sup>1</sup>         | t <sub>TRK</sub>        | CHG_TMR_PERIOD = 60 minutes and 600 minutes                                                                                              |      | 60   |      | min  |

| Fast Charge Timer <sup>1</sup>            | <b>t</b> <sub>CHG</sub> | CHG_TMR_PERIOD = 60 minutes and 600 minutes                                                                                              |      | 600  |      | min  |

| Charge Complete Timer                     | t <sub>END</sub>        | $V_{BSNS} = V_{TRM}$ , $EN_{TEND} = 1$ bit, register set                                                                                 |      | 7.5  |      | min  |

| Deglitch Timer                            | t <sub>DG</sub>         | Applies to V <sub>TRM</sub> , V <sub>RCH</sub> , I <sub>END</sub> , V <sub>WEAK</sub> , V <sub>TRK_DEAD</sub> , and V <sub>VBUS</sub> ok |      | 31   |      | ms   |

| Safety Timer                              | t <sub>SAFE</sub>       |                                                                                                                                          | 36   | 40   | 44   | min  |

| Reset Timeout Period                      | t <sub>RP</sub>         |                                                                                                                                          |      | 200  |      | ms   |

| MR for Shipment Mode                      | t <sub>SH</sub>         |                                                                                                                                          |      | 200  |      | ms   |

| Watchdog Timer <sup>1</sup>               | t <sub>WD</sub>         |                                                                                                                                          |      | 12.5 |      | sec  |

| I <sup>2</sup> C (SCL AND SDA)            |                         |                                                                                                                                          |      |      |      |      |

| Maximum Voltage on Digital Inputs         | $V_{DIN\_MAX}$          |                                                                                                                                          |      |      | 5.5  | V    |

| Low Level Input Voltage                   | VIL                     | Applies to SCL, SDA                                                                                                                      |      |      | 0.4  | V    |

| High Level Input Voltage                  | V <sub>IH</sub>         | Applies to SCL, SDA                                                                                                                      | 1.2  |      |      | V    |

| Low Level Output Voltage                  | V <sub>OL</sub>         | Applies to SDA, I <sub>SDA_SINK</sub> = 2 mA                                                                                             |      |      | 0.4  | V    |

| ĪNT, RESET, PGOOD1, PGOOD2                |                         |                                                                                                                                          |      |      |      |      |

| Leakage Current                           | I <sub>LOGO LEAK</sub>  | I <sub>LOGO</sub> = 1 mA                                                                                                                 |      | 10   | 150  | nA   |

| Output Low Voltage                        | V <sub>LOGO_LOW</sub>   | $V_{LOGO} = 5 \text{ V}$                                                                                                                 |      | 90   | 200  | mV   |

| ENCHG, EN1, EN2, STP, MR, ENSD            |                         |                                                                                                                                          |      |      |      |      |

| Input Voltage Threshold                   |                         |                                                                                                                                          |      |      |      |      |

| High                                      | VIH                     |                                                                                                                                          | 1.2  |      |      | ٧    |

| Low                                       | V <sub>IL</sub>         |                                                                                                                                          |      |      | 0.4  | ٧    |

| Input Leakage Current                     | I <sub>EN</sub> LEAKAGE |                                                                                                                                          |      |      | 150  | nA   |

$<sup>^1</sup>$  These values are programmable via  $l^2$ C. Values are given with default register values.  $^2$  Specification is not production tested but is supported by characterization data at initial product release.

### **BATTERY MONITOR SPECIFICATIONS**

$-40^{\circ}C < T_{J} < +85^{\circ}C, \ V_{ISOB} = 3.8 \ V, \ C_{1} = 2.2 \ \mu\text{F}, \ C_{2} = 1 \ \mu\text{F}, \ C_{3} = C_{4} = 10 \ \mu\text{F}, \ \text{all registers are at default values, unless otherwise noted.}$

Table 2.

| Parameter                                                  | Symbol                     | Test Conditions/Comments | Min   | Тур  | Max   | Unit |

|------------------------------------------------------------|----------------------------|--------------------------|-------|------|-------|------|

| BATTERY VOLTAGE SENSING                                    |                            |                          |       |      |       |      |

| Analog-to-Digital Converter (ADC) Reading<br>Voltage Range |                            |                          | 0     |      | 4.8   | V    |

| ADC Reading Voltage Resolution                             |                            | Based on 12-bit ADC      |       | 1.17 |       | mV   |

| ADC Reading Voltage Accuracy                               |                            | T <sub>J</sub> = 25°C    | -12.5 |      | +12.5 | mV   |

|                                                            |                            |                          | -1    |      | +1    | %    |

| UVLO Threshold                                             |                            |                          |       |      |       |      |

| Rising                                                     | Vuvlo_fg_rise              |                          |       | 2.7  | 2.8   | V    |

| Falling                                                    | Vuvlo_fg_fall              |                          | 2.48  | 2.58 |       | V    |

| BATTERY OVERDISCHARGE MONITORING                           |                            |                          |       |      |       |      |

| Undervoltage Rising Threshold                              | V <sub>BPUV_FALL</sub>     |                          | -1.5  |      | +1.5  | %    |

| Undervoltage Falling Threshold Hysteresis                  | V <sub>BPUV_FALL_HYS</sub> | HYS_UV_DISCH = 2%        |       | 2    |       | %    |

| Undervoltage Deglitch Timer                                | T <sub>BPUV_DIS</sub>      | DGT_UV_DISCH = 30 ms     |       | 30   |       | ms   |

| Overdischarge Current Threshold                            | I <sub>BPOC_DIS</sub>      | OC_DISCH = 600 mA        | 480   | 600  | 700   | mA   |

| Overdischarge Current Deglitch Timer                       | T <sub>BPOC_DIS</sub>      | DGT_OC_DISCH = 5 ms      |       | 5    |       | ms   |

| Hiccup Off Time                                            | T <sub>DIS_HCP</sub>       |                          |       | 200  |       | ms   |

| BATTERY OVERCHARGE MONITORING                              |                            | $V_{VBUS} = 5 V$         |       |      |       |      |

| Overvoltage Rising Threshold                               | $V_{BPOV\_RISE}$           |                          | -1.5  |      | +1.5  | %    |

| Overvoltage Falling Threshold Hysteresis                   | V <sub>BPOV_RISE_HYS</sub> | HYS_OV_CHG = 2%          |       | 2    |       | %    |

| Overvoltage Deglitch Timer                                 | $T_{BPOV\_CHG}$            | DGT_OV_CHG = 0.5 sec     |       | 0.5  |       | sec  |

| Overcurrent Threshold                                      | I <sub>BPOC</sub>          | OC_CHG = 150 mA          | 130   | 150  | 170   | mA   |

| Overcurrent Deglitch Time                                  | $T_{BPOC\_CHG}$            | DGT_OC_CHG = 10 ms       |       | 10   |       | ms   |

| Hiccup Off Time                                            | T <sub>CHG_HCP</sub>       |                          |       | 200  |       | ms   |

#### **BUCK REGULATOR SPECIFICATIONS**

$T_J = -40$  °C to +85 °C, voltage of the VIN1 pin ( $V_{VIN1}$ ) = voltage of the VSYS pin ( $V_{VSYS}$ ) = 3.8 V, output options range ( $V_{OUT1}$ ) = 1.2 V,  $C_5 = C_6 = 10 \ \mu\text{F}$ ,  $L1 = 4.7 \ \mu\text{H}$ , all registers are at default values, unless otherwise noted.

Table 3.

| Parameter                                                   | Symbol                     | Test Conditions/Comments                   | Min  | Тур  | Max  | Unit |

|-------------------------------------------------------------|----------------------------|--------------------------------------------|------|------|------|------|

| UVLO THRESHOLD                                              |                            |                                            |      |      |      |      |

| Rising                                                      | $V_{\text{UVLO1\_RISE}}$   |                                            |      | 2.3  | 2.35 | V    |

| Falling                                                     | $V_{\text{UVLO1\_FALL}}$   |                                            | 2.15 | 2.2  |      | V    |

| OSCILLATOR CIRCUIT                                          |                            |                                            |      |      |      |      |

| Switching Frequency in Pulse Width<br>Modulation (PWM) Mode | f <sub>SW1</sub>           |                                            | 0.85 | 1.0  | 1.15 | MHz  |

| Feedback Threshold of Frequency Fold                        | $V_{OSC\_FOLD\_RISE}$      | $V_{OUT1} = 2.5 V$                         |      | 1.25 |      | V    |

| FB1 PIN                                                     |                            |                                            |      |      |      |      |

| Output Options Range                                        | V <sub>OUT1</sub>          | Factory trim or I <sup>2</sup> C, six bits | 0.6  |      | 3.75 | V    |

| PWM Mode                                                    |                            |                                            |      |      |      |      |

| Fixed Voltage Identification (VID) Code<br>Voltage Accuracy | V <sub>FB1_PWM_FIX</sub>   |                                            | -2   |      | +2   | %    |

| Hysteresis Mode                                             |                            |                                            |      |      |      |      |

| Fixed VID Code Threshold Accuracy                           | $V_{FB1\_HYS\_FIX}$        |                                            | -2   |      | +2   | %    |

| Hysteresis of Threshold Accuracy                            | V <sub>FB1_HYS (HYS)</sub> |                                            |      | 1    |      | %    |

| Feedback Bias Current                                       | I <sub>FB1</sub>           | $V_{OUT1} = 0.6 V$                         |      | 50   |      | nA   |

| SW1 PIN                                                     |                            |                                            |      |      |      |      |

| High-Side Power FET On Resistance                           | R <sub>DS (ON) H</sub>     | Pin to pin measurement                     |      | 280  | 380  | mΩ   |

| Low-Side Power FET On Resistance                            | R <sub>DS</sub> (ON) L     | Pin to pin measurement                     |      | 260  | 380  | mΩ   |

Rev. 0 | Page 6 of 59

| Parameter                                        | Symbol               | Test Conditions/Comments            | Min | Тур  | Max  | Unit |

|--------------------------------------------------|----------------------|-------------------------------------|-----|------|------|------|

| Current Limit in PWM Mode                        | I <sub>LIM_PWM</sub> | PWM mode                            | 850 | 1000 | 1150 | mA   |

| Peak Current in Hysteresis Mode                  | I <sub>LIM_HYS</sub> | Hysteresis mode, BUCK_ILIM = 200 mA | 160 | 200  | 240  | mA   |

| Minimum On Time <sup>1</sup>                     | t <sub>MIN_ON</sub>  |                                     |     | 60   |      | ns   |

| SOFT START                                       |                      |                                     |     |      |      |      |

| Default Soft Start Time                          | t <sub>SS1</sub>     | BUCK_SS[1:0] = 1 ms                 |     | 1    |      | ms   |

| C <sub>OUT1</sub> DISCHARGE SWITCH ON RESISTANCE | R <sub>DIS1</sub>    |                                     |     | 255  |      | Ω    |

<sup>&</sup>lt;sup>1</sup> Guaranteed by design.

### **BUCK BOOST REGULATOR SPECIFICATIONS**

$T_J = -40$  °C to +85 °C, voltage of the VIN2 pin ( $V_{VIN2}$ ) =  $V_{VSYS}$  = 3.8 V, voltage of the VOUT2 pin ( $V_{VOUT2}$ ) = 5 V,  $C_7$  =  $C_8$  = 10  $\mu$ F, L2 = 4.7  $\mu$ H, all registers are at default values, unless otherwise noted.

Table 4.

| Parameter                                        | Symbol                     | Test Conditions/Comments                   | Min  | Тур  | Max  | Unit |

|--------------------------------------------------|----------------------------|--------------------------------------------|------|------|------|------|

| UVLO THRESHOLD                                   |                            |                                            |      |      |      |      |

| Rising                                           | Vuvlo2_rising              |                                            |      | 2.3  | 2.36 | V    |

| Falling                                          | V <sub>UVLO2_FALLING</sub> |                                            | 2.11 | 2.16 |      | V    |

| OUTPUT VOLTAGE RANGE                             |                            | Factory trim or I <sup>2</sup> C, six bits | 1.8  |      | 5.5  | V    |

| Output Voltage Accuracy                          | $V_{VOUT2}$                |                                            | -2   |      | +2   | %    |

| Hysteresis of Threshold Accuracy                 | $V_{\text{VOUT2\_HYS}}$    |                                            |      | 1    |      | %    |

| SW2A AND SW2B PINS                               |                            |                                            |      |      |      |      |

| High-Side FET Resistance – A (SW2A)              | R <sub>DS(ON)1_2A-H</sub>  |                                            |      | 354  | 470  | mΩ   |

| Low-Side FET Resistance – A (SW2A)               | R <sub>DS(ON)1_2A-L</sub>  |                                            |      | 250  | 360  | mΩ   |

| High-Side FET Resistance – B (SW2B)              | R <sub>DS(ON)1_2B-H</sub>  |                                            |      | 290  | 400  | mΩ   |

| Low-Side FET Resistance – B (SW2B)               | R <sub>DS(ON)1_2B-L</sub>  |                                            |      | 230  | 330  | mΩ   |

| Peak Current-Limit Threshold                     | I <sub>TH(ILIM1_2)</sub>   | BUCKBST_ILIM = 200 mA                      | 160  | 200  | 240  | mA   |

| SOFT START TIME                                  |                            |                                            |      |      |      |      |

| Soft Start Time                                  | t <sub>SS2</sub>           | BUCKBST_SS[0:1] = 1 ms                     |      | 1    |      | ms   |

| Programmable Soft Start Range                    |                            |                                            | 1    |      | 512  | ms   |

| C <sub>OUT2</sub> Discharge Switch On Resistance | R <sub>DIS2</sub>          |                                            |      | 255  |      | Ω    |

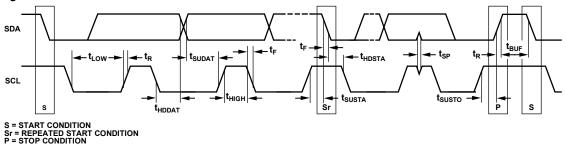

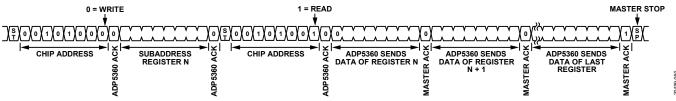

### I<sup>2</sup>C-COMPATIBLE INTERFACE TIMING SPECIFICATIONS

Table 5.

| Parameter                                                    | Symbol             | Min | Тур | Max | Unit |

|--------------------------------------------------------------|--------------------|-----|-----|-----|------|

| I <sup>2</sup> C-COMPATIBLE INTERFACE                        |                    |     |     |     |      |

| Capacitive Load, Each Bus Line                               | Cs                 |     |     | 400 | pF   |

| SCL Clock Frequency                                          | f <sub>SCL</sub>   |     |     | 400 | kHz  |

| SCL High Time                                                | t <sub>HIGH</sub>  | 0.6 |     |     | μs   |

| SCL Low Time                                                 | t <sub>LOW</sub>   | 1.3 |     |     | μs   |

| Data Setup Time                                              | tsudat             | 100 |     |     | ns   |

| Data Hold Time <sup>1</sup>                                  | t <sub>HDDAT</sub> | 0   |     | 0.9 | μs   |

| Setup Time for Repeated Start                                | t <sub>SUSTA</sub> | 0.6 |     |     | μs   |

| Hold Time for Start/Repeated Start                           | t <sub>HDSTA</sub> | 0.6 |     |     | μs   |

| Bus Free Time Between a Stop Condition and a Start Condition | t <sub>BUF</sub>   | 1.3 |     |     | μs   |

| Setup Time for Stop Condition                                | <b>t</b> susto     | 0.6 |     |     | μs   |

| Rise Time of SCL/SDA                                         | t <sub>R</sub>     | 20  |     | 300 | ns   |

| Fall Time of SCL/SDA                                         | t <sub>F</sub>     | 20  |     | 300 | ns   |

| Pulse Width of Suppressed Spike                              | t <sub>SP</sub>    | 0   |     | 50  | ns   |

<sup>&</sup>lt;sup>1</sup> A master device must provide a hold time of at least 300 ns for the SDA signal to bridge the undefined region of the falling edge of SCL. See Figure 2 for more information.

## Timing Diagram

Figure 2. I<sup>2</sup>C Timing Diagram

## RECOMMENDED INPUT AND OUTPUT CAPACITANCE AND INDUCTANCE

## Table 6.

| Parameter                    | Test Conditions/Comments | Min  | Тур | Max | Unit |

|------------------------------|--------------------------|------|-----|-----|------|

| CAPACITANCE                  |                          |      |     |     |      |

| VBUS Capacitance             | Effective capacitance    | 1.0  | 2.2 |     | μF   |

| VDD Pin Capacitance          | Effective capacitance    | 0.47 | 1.0 | 10  | μF   |

| VSYS Pin Total Capacitance   | Effective capacitance    | 4.7  | 10  |     | μF   |

| ISOB Pin Total Capacitance   | Effective capacitance    | 4.7  | 10  |     | μF   |

| VIN1 Pin Total Capacitance   | Effective capacitance    | 2.2  | 10  |     | μF   |

| VIN2 Pin Total Capacitance   | Effective capacitance    | 2.2  | 10  |     | μF   |

| VOUT1 Node Total Capacitance | Effective capacitance    | 1    | 10  |     | μF   |

| VOUT2 Total Capacitance      | Effective capacitance    | 1    | 10  |     | μF   |

| INDUCTANCE                   |                          |      |     |     |      |

| Buck Inductance              |                          | 2.2  | 4.7 | 6.8 | μΗ   |

| Buck Boost Inductance        |                          | 2.2  | 4.7 | 6.8 | μΗ   |

#### **ABSOLUTE MAXIMUM RATINGS**

#### Table 7.

| Tubic / .                                                                                           |                  |

|-----------------------------------------------------------------------------------------------------|------------------|

| Parameter                                                                                           | Rating           |

| VBUS to PGND1                                                                                       | −0.5 V to +20 V  |

| PGND1, PGND2 to AGNDx                                                                               | -0.3 V to +0.3 V |

| All Other Pins to AGNDx                                                                             | −0.3 V to +6 V   |

| Continuous Drain Current, Battery Supplementary Mode, from ISOB to VSYS, $T_J = 85^{\circ}\text{C}$ | 1.1 A            |

| Storage Temperature Range                                                                           | −65°C to +150°C  |

| Operating Junction Temperature Range                                                                | −40°C to +85°C   |

| Soldering Conditions                                                                                | JEDEC J-STD-020  |

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

#### THERMAL RESISTANCE

Thermal performance is directly linked to printed circuit board (PCB) design and operating environment. Careful attention to PCB thermal design is required.

$\theta_{JA}$  is the natural convection, junction to ambient, thermal resistance measured in a one cubic foot sealed enclosure.  $\theta_{JC}$  is the junction to case thermal resistance.

**Table 8. Thermal Resistance**

| Package Type | θ <sub>JA</sub> | θ <sub>JC</sub> | Unit |

|--------------|-----------------|-----------------|------|

| CB-32-2      | 50              | 0.35            | °C/W |

#### **Maximum Power Dissipation**

The maximum safe power dissipation in the ADP5360 package is limited by the associated rise in junction temperature (T<sub>i</sub>) on the die. At approximately 150°C, which is the glass transition temperature, the plastic changes properties. Even temporarily exceeding this temperature limit can change the stresses that the package exerts on the die, permanently shifting the parametric performance of the ADP5360. Exceeding a junction temperature of 175°C for an extended period of time can result in changes in the silicon devices that potentially cause failure.

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

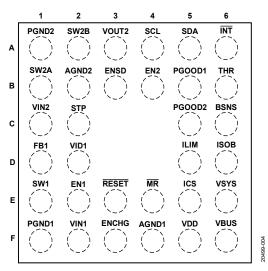

## PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 3. Pin Configuration (Top View)

**Table 9. Pin Function Descriptions**

| Pin No. | Mnemonic | Description                                                                                                                                                                                                                         |

|---------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1      | PGND2    | Power Ground for the Buck Boost Regulator.                                                                                                                                                                                          |

| A2      | SW2B     | Switching Mode for Buck Boost Regulator.                                                                                                                                                                                            |

| A3      | VOUT2    | Buck Boost Regulator Output Pin.                                                                                                                                                                                                    |

| A4      | SCL      | I <sup>2</sup> C Serial Clock. Requires an external pull-up resistor.                                                                                                                                                               |

| A5      | SDA      | I <sup>2</sup> C Serial Data. Requires an external pull-up resistor.                                                                                                                                                                |

| A6      | ĪNT      | Processor Interrupt (Active Low). Requires an external pull-up resistor. If this pin is not used, it can be left floating.                                                                                                          |

| B1      | SW2A     | Switching Mode for Buck Boost Regulator.                                                                                                                                                                                            |

| B2      | AGND2    | Analog Ground.                                                                                                                                                                                                                      |

| B3      | ENSD     | Shutdown Mode Select Pin. This pin disables shutdown mode when it is low and enables shutdown mode when it high.                                                                                                                    |

| B4      | EN2      | Enable Pin for Buck Boost Regulators.                                                                                                                                                                                               |

| B5      | PGOOD1   | Power-Good Signal Output. This open-drain output is the power-good signal for the selected VBUSOK, BATOK, CHG_CMPLT, VOUT2OK, or VOUT1OK bits.                                                                                      |

| B6      | THR      | Battery Pack Thermistor Connection.                                                                                                                                                                                                 |

| C1      | VIN2     | Input Power for Buck Regulator.                                                                                                                                                                                                     |

| C2      | STP      | Stop Switching for Selected Channel.                                                                                                                                                                                                |

| C5      | PGOOD2   | Power-Good Signal Output. This open-drain output is the power-good signal for the selected VBUSOK, BATOK, CHG_CMPLT, VOUT2OK, or VOUT1OK bits.                                                                                      |

| C6      | BSNS     | Battery Voltage Sense Pin.                                                                                                                                                                                                          |

| D1      | FB1      | Feedback Sensing Input for the Buck Regulator.                                                                                                                                                                                      |

| D2      | VID1     | Buck Regulator Output Voltage Configure Pin. Connect a resistor from VID1 to AGND1 and AGND2 to program the buck regulator default output voltage. Float the pin to disable the pin select feature and use the register default set |

| D5      | ILIM     | Input Current-Limit Select Pin. Connect a resistor to AGND1 and AGND2 to set the default input current-limit level Float the pin to disable the pin select feature and use the register default set.                                |

| D6      | ISOB     | Battery Supply Side Input to Internal Isolation FET.                                                                                                                                                                                |

| E1      | SW1      | Switching Mode for Buck Regulator.                                                                                                                                                                                                  |

| E2      | EN1      | Hardware Enable Pin for Buck Regulators.                                                                                                                                                                                            |

| E3      | RESET    | Reset Output.                                                                                                                                                                                                                       |

| E4      | MR       | Manual Reset Input Pin.                                                                                                                                                                                                             |

| E5      | ICS      | Charge Current Set Pin. Connect one resistor to ground to set the default charge current. Float the pin to disable the pin select feature and use the register default set.                                                         |

| E6      | VSYS     | Linear Charger Supply Side Input to the Internal Isolation FET.                                                                                                                                                                     |

| F1      | PGND1    | Power Ground for the Buck Regulator.                                                                                                                                                                                                |

| Pin No. | Mnemonic | Description                              |

|---------|----------|------------------------------------------|

| F2      | VIN1     | Input Power for Buck Regulator.          |

| F3      | ENCHG    | Logic Input for Enable Charger Function. |

| F4      | AGND1    | Analog Ground.                           |

| F5      | VDD      | Internal Circuit Power Supply.           |

| F6      | VBUS     | Power Connection to USB VBUS.            |

## TYPICAL PERFORMANCE CHARACTERISTICS

$V_{VBUS} = 5.0 \text{ V}, V_{ISOB} = 3.6 \text{ V}, C_1 = 2.2 \text{ }\mu\text{F}, C_2 = 1 \text{ }\mu\text{F}, C_3 = C_4 = 10 \text{ }\mu\text{F}, C_5 = C_6 = 10 \text{ }\mu\text{F}, C_7 = C_8 = 10 \text{ }\mu\text{F}, L1 = L2 = 4.7 \text{ }\mu\text{H}, \text{ all registers are at default values unless otherwise noted.}$

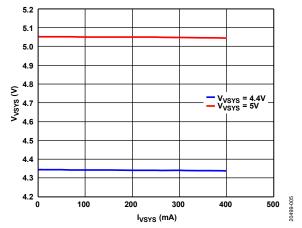

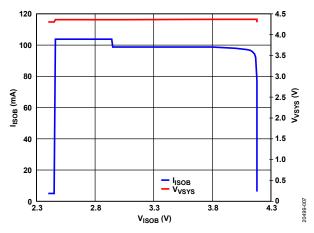

Figure 4. VSYS Load Regulation,  $V_{VSYS} = 4.4 \text{ V}$  and 5 V,  $V_{VBUS} = 5.5 \text{ V}$ ,  $I_{VSYS}$  from 1 mA to 400 mA, No Charging

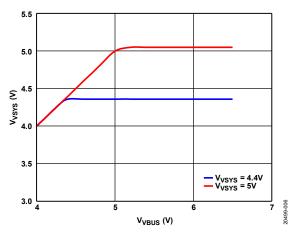

Figure 5. VSYS Line Regulation,  $V_{VSYS} = 4.4 V$  and 5 V, No Charging

Figure 6. Charge Profile,  $V_{TRM} = 4.2 \text{ V}$ ,  $I_{CHG} = 100 \text{ mA}$

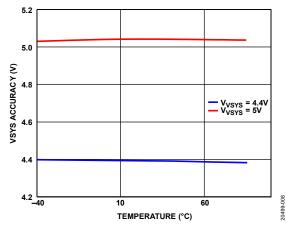

Figure 7. VSYS Accuracy vs. Temperature,  $V_{VBUS} = 5.5 V$

Figure 8. ISOFET Resistor vs. Battery Voltage

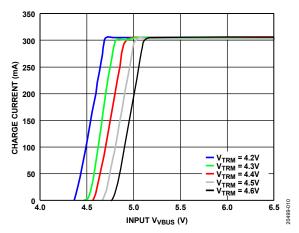

Figure 9. Charge Current vs. Input  $V_{VBUS}$ ,  $I_{CHG} = 300 \text{ mA}$

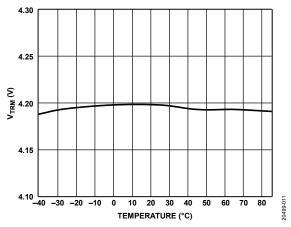

Figure 10.  $V_{TRM}$  vs. Temperature,  $V_{TRM} = 4.2 \text{ V}$

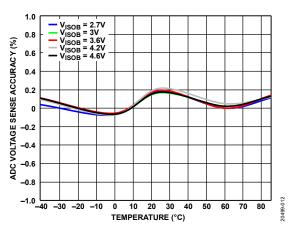

Figure 11. ADC Voltage Sense Accurarcy vs. Temperature, V<sub>VBUS</sub> = 0 V

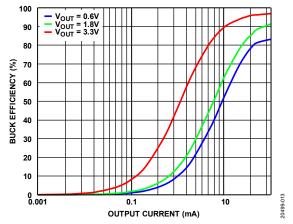

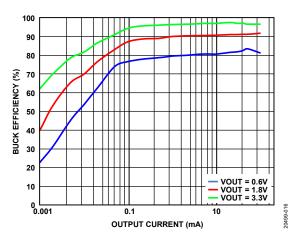

Figure 12. Buck Efficiency vs. Output Current,  $V_{VIN1} = 3.8 \text{ V}$ , PWM Mode

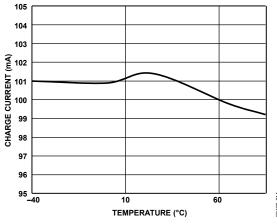

Figure 13. Charge Current vs. Temperature, I<sub>CHG</sub> = 100 mA

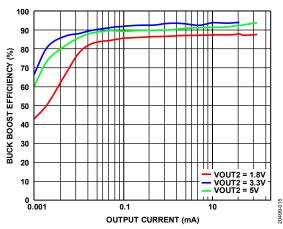

Figure 14. Buck Boost Efficiency vs. Output Current,  $V_{VIN2} = 3.8 \text{ V}$

Figure 15. Buck Efficiency vs. Output Current,  $V_{VIN1} = 3.8 V$ , Hysteresis Mode

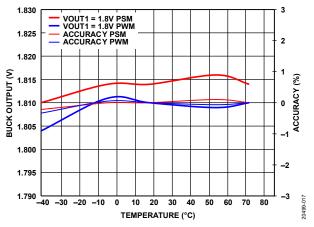

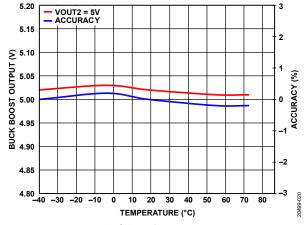

Figure 16. Buck Output vs. Temperature

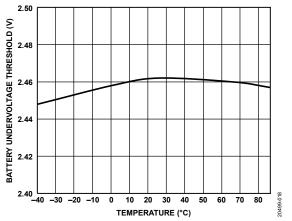

Figure 17. Battery Undervoltage Threshold vs. Temperature, BAT\_UV = 2.5 V

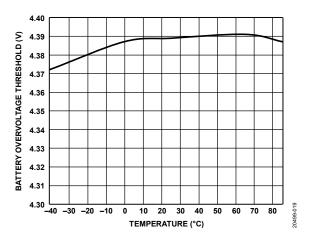

Figure 18. Battery Overvoltage Threshold vs. Temperature, BAT\_OV = 4.3 V

Figure 19. Buck Boost Output vs. Temperature

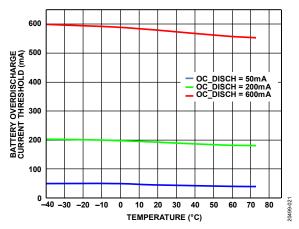

Figure 20. Battery Overdischarge Current Threshold vs. Temperature,  $V_{\text{ISOB}} = 3.8 \text{ V}$

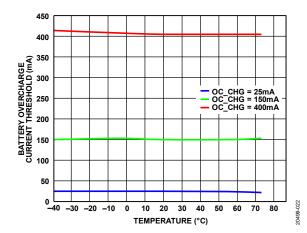

Figure 21. Battery Overcharge Current Threshold vs. Temperature,  $V_{ISOB} = 3.8 \text{ V}$

Figure 22. ISOB Quiescent Current vs. Temperature

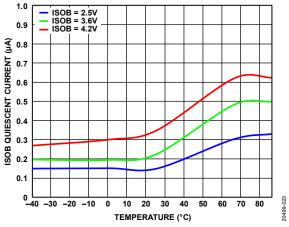

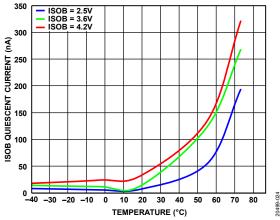

Figure 23. ISOB Quiescent Current vs. Temperature

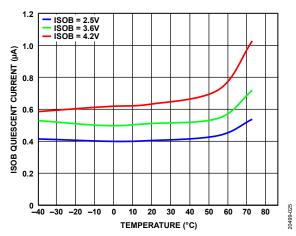

Figure 24. ISOB Quiescent Current vs. Temperature, Fuel Gauge Sleep Mode Enabled, Battery Protection Enabled, Buck Enabled, Buck Boost Enabled

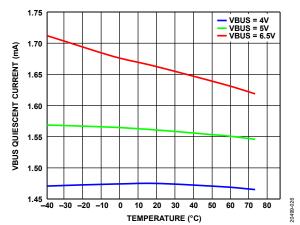

Figure 25. VBUS Quiescent Current vs. Temperature

#### **TYPICAL WAVEFORMS**

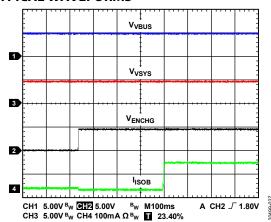

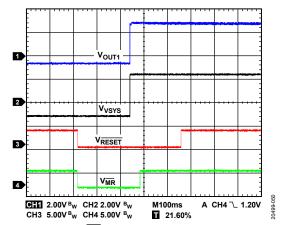

Figure 26. Charge Startup,  $V_{VBUS} = 5 V$ ,  $V_{ISOB} = 3.8 V$ ,  $I_{ILIM} = 200 \text{ mA}$ ,  $I_{CHG} = 100 \text{ mA}$

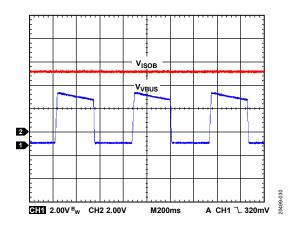

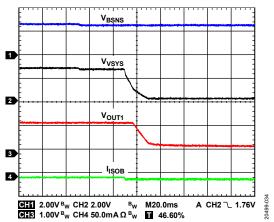

Figure 27. USB Connect and Start Charge,  $V_{VBUS} = 5 V$ ,  $V_{ISOB} = 3.8 V$ ,  $I_{CHG} = 100 \text{ mA}$

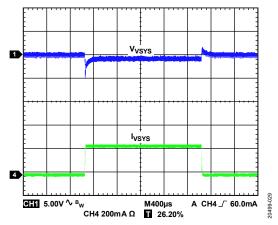

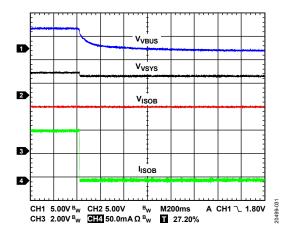

Figure 28. VSYS Load Transient,  $I_{VSYS} = 50 \text{ mA}$  to 300 mA

Figure 29. Battery Detection Waveform

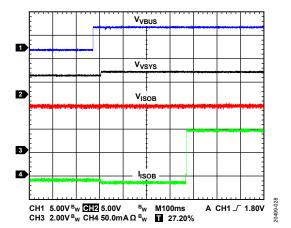

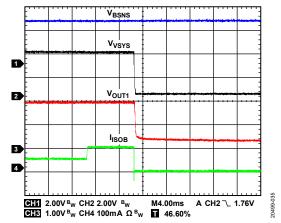

Figure 30. USB Disconnect and End Charge,  $V_{VBUS} = 5$  V,  $V_{ISOB} = 3.8$  V,  $I_{CHG} = 100$  mA

Figure 31. Adaptive Charge Current, VADPICHG[2:0] = 4.6 V,  $V_{VBUS} = 5 V$  with  $10 \Omega$  Impedance,  $I_{CHG} = 100 \text{ mA}$

Figure 32. Battery Overvoltage Protection Waveform, V<sub>VBUS</sub> = 5 V, OV\_CHG = 4.3 V, DGT\_OV\_CHG = 0.5 sec

Figure 33. Battery Undervoltage Protection Waveform,  $V_{VBUS} = 0 V$ ,  $UV_DISCH = 2.5 V$ ,  $DGT_UV_DISCH = 30 ms$

Figure 34. Battery Discharge Overcurrent Waveform,  $V_{VBUS} = 0 \text{ V}, V_{ISOB} = 3.8 \text{ V}, OC\_DISCH = 100 \text{ mA}, DGT\_OC\_DISCH = 10 \text{ ms}$

Figure 35. Battery Charge Overcurrent Waveform,  $V_{VBUS} = 5 V$ ,  $V_{ISOB} = 3.8 V$ , OC\_CHG = 150 mA, DGT\_OC\_CHG = 10 ms

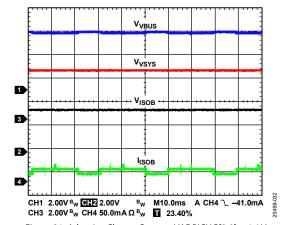

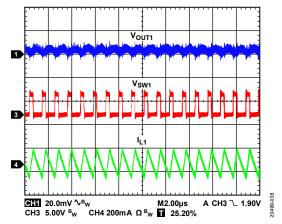

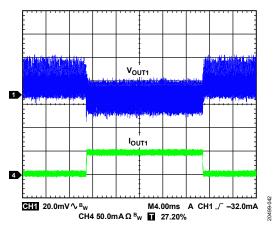

Figure 36. Buck Steady Hysteresis Waveform, Hysteresis Mode,  $V_{VIN2} = 3.8 \text{ V}$ ,  $V_{OUT1} = 1.2 \text{ V}$ , Buck Output Current ( $I_{OUT1}$ ) = 1 mA

Figure 37. Buck Steady PWM Waveform, PWM Mode,  $V_{VIN1} = 3.8 \text{ V}, V_{OUT1} = 1.2 \text{ V}, I_{OUT1} = 1 \text{ mA}$

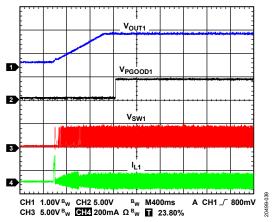

Figure 38. Buck Output Soft Start, Set EN\_BUCK High, PWM Mode,  $V_{VIN1} = 3.8 \text{ V}$ ,  $V_{OUT1} = 1.2 \text{ V}$ , PGOOD1 Mask to VOUT1,  $I_{OUT1} = 1 \text{ mA}$ , SS1 = 8 ms

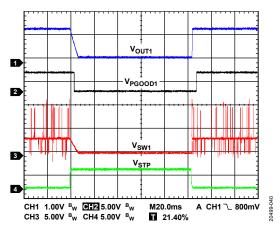

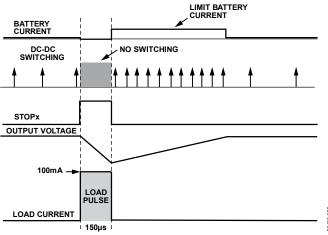

Figure 39. Buck Stop Function Waveform,  $V_{VIN1} = 3.8 \text{ V}$ ,  $V_{OUT1} = 1.2 \text{ V}$ , Hysteresis Mode, PGOOD1 Mask to VOUT1, STP\_BUCK = 1 Bit

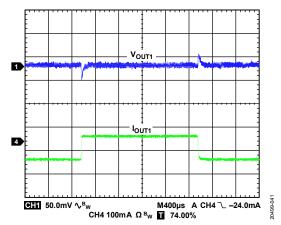

Figure 40. Buck Output Transient Waveform,  $V_{VIN1}=3.8~V$ ,  $V_{OUT1}=1.2~V$ ,  $I_{OUT1}=1~mA$  to 100 mA, PWM Mode

Figure 41. Buck Output Transient Waveform,  $V_{VIN1} = 3.8 \text{ V}$ ,  $V_{OUT1} = 1.2 \text{ V}$ ,  $I_{OUT1} = 1 \text{ mA to } 100 \text{ mA}$ , Hysteresis Mode

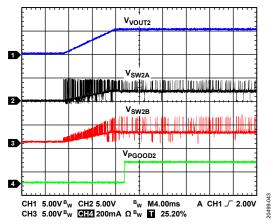

Figure 42. Buck Boost Output Soft Start Waveform,  $V_{VIN2} = 3.8 \text{ V}$ ,  $V_{OUT2} = 5 \text{ V}$ ,  $BUCKBST\_SS[0:1] = 8 \text{ ms}$ ,  $Buck Boost Output Current (<math>I_{OUT2}$ ) = 1 mA, PGOOD2 Mask to VOUT2

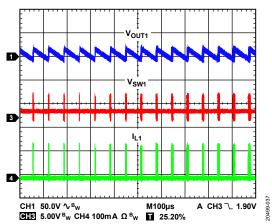

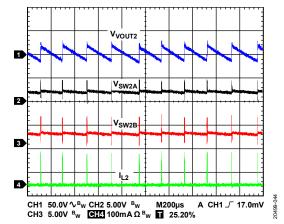

Figure 43. Buck Boost Steady Waveform,  $V_{VIN2} = 3.8 \text{ V}$ ,  $V_{OUT2} = 5 \text{ V}$ ,  $I_{OUT2} = 1 \text{ mA}$

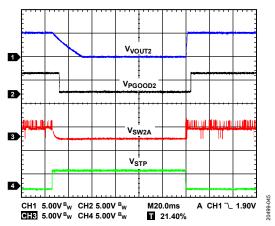

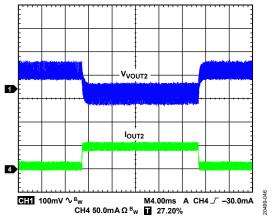

Figure 44. Buck Boost Stop Function Waveform,  $V_{VIN2} = 3.8 \text{ V}$ ,  $V_{OUT2} = 5 \text{ V}$ , PGOOD2 Mask to VOUT2,  $STP\_BUCKBST = 1$  bit

Figure 45. Buck Boost Output Transient Waveform,  $V_{VIN2} = 3.8 \text{ V}$ ,  $V_{OUT2} = 3.3 \text{ V}$ ,  $I_{OUT2} = 1 \text{ mA to } 50 \text{ mA}$

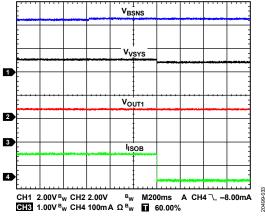

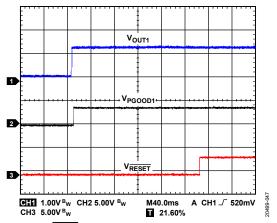

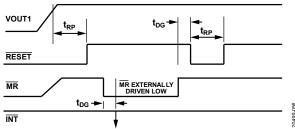

Figure 46.  $\overline{RESET}$  Output and VOUT1,  $V_{ISOB} = 3.8 \text{ V}$ ,  $V_{OUT1} = 1.2 \text{ V}$ ,  $RESET\_TIME = 200 \text{ ms}$ , PGOOD1 Mask to VOUT1

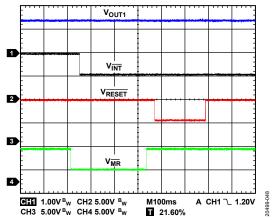

Figure 47.  $\overline{MR}$  Press to Trigger Interrupt and  $\overline{RESET}$ , EN\_WD\_INT = 1 bit, RESET\_TIME = 200 ms

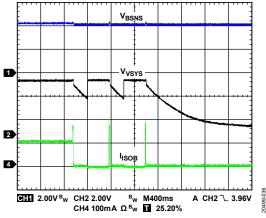

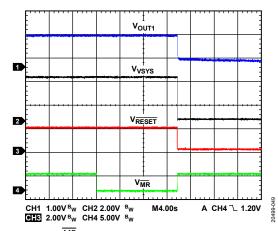

Figure 48. Press  $\overline{MR}$  >12 sec to Enter Shipment Mode, EN\_MR\_SD = 1 bit, ENSD Pin is High

Figure 49. Press MR to Exit Shipment Mode, ENSD Pin is High

## THEORY OF OPERATION

#### **BATTERY CHARGER**

#### **Charger Introduction**

The ADP5360 integrates a fully  $I^2C$ -programmable charger for single cell Li-Ion/Li-Poly batteries suitable for a wide range of portable applications.

The linear charger architecture enables up to 500 mA of output current on the system power supply and up to 320 mA of charge current into the battery from a dedicated charger.

The charger of the ADP5360 operates from an input voltage up to 6.8 V, but is tolerant of voltages up to 20 V to alleviate the concern of USB bus spiking during disconnection or connection scenarios.

The ADP5360 features an internal FET between the linear charger output and the battery node to permit battery isolation and system powering in a dead battery or no battery scenario, which allows for immediate system function when connected to a USB power supply.

The charger of the ADP5360 enables charging via the mini VBUS pin (F6 pin) from a wall charger, car charger, or USB host port. Based on the type of USB source, which is detected by an external USB detection device, the ADP5360 can be set to apply the proper current limit for optimal charging and USB compliance. The USB charger permits correct operation under all USB compliant sources including wall chargers, host chargers, hub chargers, and standard hosts and hubs.

A processor controls the USB charger using the I<sup>2</sup>C to program the charging current and numerous other parameters, including:

- Trickle charge current level and voltage threshold.

- Fast charge (constant current) current level.

- Fast charge (constant voltage) termination voltage level.

- Fast charge safety timer period.

- Weak battery threshold detection.

- End of charge current level for charge completion.

- Recharge voltage threshold.

- VBUS input current limit.

#### Input Current Limit and USB Compatibility

The VBUS input current limit can be programmed via an internal I $^2$ C ILIM register from 50 mA to 500 mA, ensuring compatibility with different requirements. An external resistor from the ILIM pin to ground can also set the input current limit as the default. Floating the ILIM pin activates the register default value when powering up.

Table 10. VBUS Input Current-Limit Default Set with ILIM Pin

| riii                             |           |

|----------------------------------|-----------|

| Register                         | ILIM (mA) |

| $R_{ILIM} = 100 \text{ k}\Omega$ | 50        |

| $R_{ILIM} = 68 \text{ k}\Omega$  | 100       |

| $R_{ILIM} = 47 \text{ k}\Omega$  | 150       |

| $R_{ILIM} = 36 \text{ k}\Omega$  | 200       |

| $R_{ILIM} = 27 \text{ k}\Omega$  | 250       |

| $R_{ILIM} = 20 \text{ k}\Omega$  | 300       |

| $R_{ILIM} = 15 \text{ k}\Omega$  | 400       |

| $R_{ILIM} = 10 \text{ k}\Omega$  | 500       |

The current limit defaults to 100 mA to allow compatibility with a USB host or hub that is not configured. To protect the USB port, this input current limit resets to a default value of 100 mA during every cycle power on the VBUS pin.

When the input current-limit feature is used, it is possible that the available input current is too low for the charger to meet the programmed charging current ( $I_{CHG}$ ), and the rate of charge is reduced. In this case, the VBUS\_ILIM flag is set.

The VBUS\_OK bit is set when the V<sub>VBUS</sub> voltage is between 3.9 V and 6.8 V and the charger is ready to start charging.

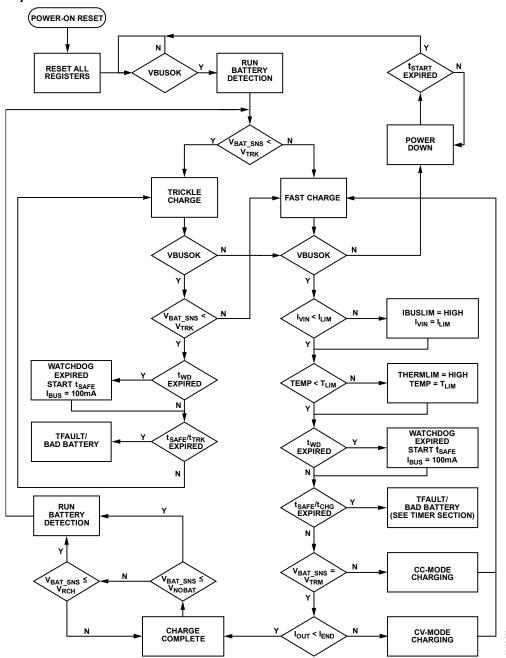

#### Trickle Charge Mode

A deeply discharged Li-Ion cell can exhibit a low cell voltage, making it unsafe to charge the cell at high current rates. The ADP5360 charger uses a trickle charge mode to raise the cell voltage to a safe level for fast charging. A cell with a voltage lower than  $V_{\text{TRK\_DEAD}}$  charges with the trickle mode current ( $I_{\text{TRK\_DEAD}}$ ). During trickle charge mode, the CHARGER\_STATUS register is set.

During trickle charging, the VSYS node is regulated to  $V_{SYS\_REG}$  by the linear regulator. The battery isolation FET is off, therefore the battery is isolated from the system power supply. The  $V_{SYS\_REG}$  output voltage is shown in Table 11.

Table 11. V<sub>SYS\_REG</sub> Output Voltage

|                                 | V <sub>SYS_REG</sub> (V)                              |                                   |  |  |  |

|---------------------------------|-------------------------------------------------------|-----------------------------------|--|--|--|

| V <sub>TRM</sub> Setting        | $V_{\text{SYSTEM}} = V_{\text{TRM}} + 200 \text{ mV}$ | $V_{\text{SYSTEM}} = 5 \text{ V}$ |  |  |  |

| $V_{TRM} \le 4.26 \text{ V}$    | 4.4 V                                                 | 5 V                               |  |  |  |

| $4.26V < V_{TRM} \le 4.36V$     | 4.5 V                                                 | 5 V                               |  |  |  |

| $4.36  V < V_{TRM} \le 4.46  V$ | 4.6 V                                                 | 5 V                               |  |  |  |

| $4.46  V < V_{TRM} \le 4.56  V$ | 4.7 V                                                 | 5 V                               |  |  |  |

| $4.56V < V_{TRM} \le 4.66V$     | 4.8 V                                                 | 5 V                               |  |  |  |

When the  $V_{VBUS}$  voltage is lower than the  $V_{SYS\_REG}$  set value, the VSYS node voltage cannot be regulated, which impacts the charged current (see Figure 9).

#### Trickle Charge Mode Timer

The duration of trickle charge mode is monitored to ensure the battery revives from the deeply discharged state. If trickle charge mode runs for longer than  $t_{\text{TRK}}$  without the cell voltage reaching  $V_{\text{TRK\_DEAD}}$ , a fault condition is assumed, and charging stops. The battery isolation FET turns off, and the VSYS node is regulated to  $V_{\text{SYS\_REG}}$  by the linear regulator. The fault condition asserts on the CHARGER\_STATUS register, allowing the user to initiate the fault recovery procedure specified in the Fault Recovery section.

#### Weak Charge Mode (Constant Current)

When the battery voltage exceeds  $V_{TRK\_DEAD}$  but is less than  $V_{WEAK}$ , the charger switches to the weak charge mode, and the VSYS node is regulated to  $V_{SYS\_REG}$  by the battery isolation FET.  $V_{SYSTEM} = 5 \text{ V}$  is not active on the output of  $V_{SYS\_REG}$  during charge mode.

During weak charge mode, the battery is charged with programmed  $I_{CHG}$  from the VSYS node through the isolation FET and the trickle current  $I_{TRK\_DEAD}$ . Due to the VBUS input current limit, the real charge current  $I_{CHG}$  from the VSYS node may be less than the programmed value. System load can share the current from the VSYS node. However, the trickle current  $I_{TRK\_DEAD}$  always charges the battery during weak charge mode.

#### Fast Charge Mode (Constant Current)

When the battery voltage exceeds  $V_{WEAK}$ , the charger switches to fast charge mode, charging the battery with the  $I_{CHG}$ . The  $I_{CHG}$  can be programmed by Register 0x04, ICH[4:0], set via  $I^2C$ . During fast charge mode (constant current), the CHARGER\_STATUS register is set. The default  $I_{CHG}$  value can be set by the external resistor ( $R_{ICS}$ ) from the ICS pin to ground. Floating the ICS pin activates the register default value when powering up.

Table 12. Charge Current Default Set Using the ICS Pin

| Register                        | I <sub>CHG</sub> (mA) |

|---------------------------------|-----------------------|

| $R_{ICS} = 100 \text{ k}\Omega$ | 10                    |

| $R_{ICS} = 68 \text{ k}\Omega$  | 50                    |

| $R_{ICS} = 47 \text{ k}\Omega$  | 80                    |

| $R_{ICS} = 36 \text{ k}\Omega$  | 100                   |

| $R_{ICS} = 27 \text{ k}\Omega$  | 150                   |

| $R_{ICS} = 20 \text{ k}\Omega$  | 200                   |

| $R_{ICS} = 15 \text{ k}\Omega$  | 250                   |

| $R_{ICS} = 10 \text{ k}\Omega$  | 300                   |

During constant current mode, other features can prevent the  $I_{\text{CHG}}$  from reaching the full programmed value. Input current limiting for USB compatibility can affect the value of  $I_{\text{CHG}}$  under certain operating conditions. The voltage on VSYS is regulated to stay at  $V_{\text{SYS\_REG}}$  by the battery isolation FET.  $V_{\text{SYSTEM}} = 5 \text{ V}$  is not active on the output of  $V_{\text{SYS\_REG}}$  during charge mode.

The ADP5360 features a dynamic charge current that is adaptive when the input VBUS voltage drops too much due to possible high internal impedance. The dynamic charge current monitors the VBUS voltage and reduces the charge current level

when the VBUS voltage falls lower than the threshold, which can be programed by I<sup>2</sup>C. When the charge current adapts due to the VBUS voltage level, the ADPICHG status bit is set high. This feature is disabled by default and can be enabled by the I<sup>2</sup>C setting.

#### Fast Charge Mode (Constant Voltage)

As the battery charges, the voltage rises and approaches the termination voltage ( $V_{TRM}$ ). The ADP5360 charger monitors the voltage on the BSNS pin to determine when charging ends. However, the internal impedance of the battery pack combined with PCB and other parasitic series resistances creates a voltage drop between the sense point at the BSNS pin and the cell terminal. To compensate for this voltage drop and ensure a fully charged cell, the ADP5360 enters a constant voltage (CV) charge mode when the BSNS voltage reaches termination voltage. The ADP5360 reduces charge current gradually as the cell continues to charge, maintaining a voltage of  $V_{TRM}$  on the BSNS pin. During fast charge mode (CV), the CHARGER\_STATUS register is set.

#### Fast Charge Mode Timer

The duration of fast charge mode is monitored to ensure that the battery is charging correctly. If the fast charge mode runs for longer than  $t_{\text{CHG}}$  without the voltage at the BSNS pin reaching  $V_{\text{TRM}}$ , a fault condition is assumed, charging stops, the battery isolation FET turns off, and the VSYS node is regulated to  $V_{\text{SYS\_REG}}$  by the linear regulator. A fault condition asserts on the CHARGER\_ STATUS register, allowing the user to initiate the fault recovery procedure specified in the Fault Recovery section.

If the fast charge mode runs for longer than  $t_{CHG}$ , and  $V_{TRM}$  has been reached on the BSNS pin but the charge current has not yet fallen lower than  $I_{END}$ , charging stops by turning off the battery isolation FET. The linear regulator still works, and the VSYS node is regulated to  $V_{SYS\_REG}$ . No fault condition is asserted in this circumstance, and the ADP5360 attains charge complete status.

#### **Safety Timer**

If the watchdog timer (see the Watchdog Timer section for more information) expires while in charger mode, the ADP5360 charger initiates the safety timer ( $t_{SAFE}$ ). Charging continues for a period of  $t_{SAFE}$ , then stops by turning off the battery isolation FET and setting the CHARGER\_STATUS register.

### **Charge Complete**

The ADP5360 charger monitors the charging current while in CV fast charge mode. When EN\_TEND is low, the current falls lower than  $I_{\text{END}}$  for  $t_{\text{DG}}$  deglitch time, and the charger is stopped by turning the battery isolation FET off. The system voltage is maintained at  $V_{\text{SYS\_REG}}$  by the linear regulator and sets the CHG\_CMPLT flag. When EN\_TEND is set to high, the charging current falls lower than  $I_{\text{END}}$  for another  $t_{\text{END}}$  time, and the charger is stopped and sets the CHG\_CMPLT flag.

#### Recharge

After the detection of charge is complete and the battery isolation FET turns off, the ADP5360 charger still monitors the BSNS pin.

If the BSNS pin voltage falls to V<sub>RCH</sub>, the charger reactivates. Under most circumstances, triggering the recharge threshold results in the charger starting in fast charge mode.

#### **Battery Charging Enable/Disable**

To enable the ADP5360 charging function, set the I<sup>2</sup>C EN\_CHG bit high or pull the ENCHG pin high. The hardware ENCHG pin is logically OR'ed with Register 0x07, ENCHG bit. If the charger is disabled, the linear regulator remains on and regulates the VSYS voltage to V<sub>SYS\_REG</sub>. The battery isolation FET turns off, and the linear regulator provides the power for the system.

#### **BATTERY ISOLATION FET**

The ADP5360 charger features an integrated battery isolation FET for power path control and battery protection. The battery isolation FET isolates a deeply discharged Li-Ion cell from the system power supply in both trickle and fast charge modes, therefore allowing the system to be powered at all times. The battery isolation FET maintains the V<sub>SYS\_REG</sub> voltage on the VSYS pin.

When VBUS is lower than  $V_{\text{VBUS\_OK}}$ , the battery isolation FET is in full conducting status.

The battery isolation FET supplements the battery to support high current functions on the system power supply when VBUS current is limited.

When the voltage on VSYS drops lower than ISOB, the battery isolation FET enters full conducting mode.

#### **BATTERY DETECTION**

#### **Battery Level Detection**

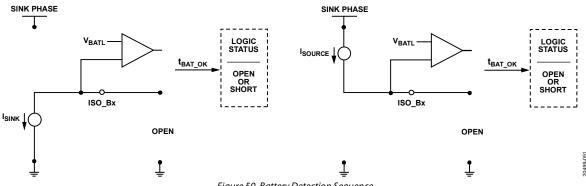

The ADP5360 charger features a battery detection mechanism to detect an absent battery. The charger actively sinks and sources current into the ISOB node when it begins to charge and voltage vs. time is detected. The sink phase detects a charged battery whereas source phase detects a discharged battery.

The sink phase (see Figure 50) sinks I<sub>SINK</sub> current from the ISOB pin and BSNS pin for typically 330 ms. If the BSNS pin is lower than  $V_{\text{BATL}}$  when the 330 ms timer expires, the charger starts the source phase. If the BSNS pin exceeds the V<sub>BATL</sub> voltage when the 330 ms timer expires, the charger begins a new charge cycle.

The source phase sources Isource current to the ISOB pin or the BSNS pin for typically 330 ms. If the BSNS pin exceeds  $V_{\mbox{\scriptsize BATH}}$ before the 330 ms timer expires, it is assumed that no battery is present. If the BSNS pin does not exceed the V<sub>BATH</sub> voltage when the 330 ms timer expires, it is assumed that a battery is present, and the charger begins a new charge cycle.

Figure 50. Battery Detection Sequence

#### **BATTERY TEMPERATURE**

#### **Battery Pack Thermistor Input**

The ADP5360 charger features battery pack temperature sensing that precludes charging when the battery pack temperature is outside of the specified range. The THR pin provides three programmable current sources: 60  $\mu A$ , 12  $\mu A$ , and 6  $\mu A$ . Accordingly, the THR pin supports 10  $k\Omega$ , 47  $k\Omega$ , and 100  $k\Omega$  negative temperature coefficient (NTC) resistors at 25°C. The THR pin is connected directly to the battery pack thermistor terminal.

When the THR function is enabled, the THR node voltage is sensed by the ADC and can be read in the 12-bit registers, THR\_V\_HIGH and THR\_V\_LOW. Calculate the external thermistor value (R<sub>NTC</sub>) using the following equation:

$$R_{NTC} = \frac{THR - V}{60 \,\mu\text{A}}$$

where:

*THR\_V* is ADC readback from the THR\_V\_HIGH and THR\_V\_LOW registers.

$60 \mu A$  is selected by the THR pin source current.

The battery temperature can be achieved by knowing the  $R_{\mbox{\scriptsize NTC}}$

When  $V_{VBUS}$  is higher than  $V_{VBUS\_OK\_RISE}$ , the THR function is forced to enable for the charger control requirement. The update

rate is 1 second. When  $V_{VBUS}$  is lower than  $V_{VBUS\_OK\_RISE}$ , set the EN\_THR bit (Register 0x0A) high to enable the THR function. The THR node voltage update rate is slowed to 30 seconds to save quiescent current.

If the battery pack thermistor is not connected directly to the THR pin, a 100 k $\Omega$  (tolerance ±20%) dummy resistor must be connected between the THR pin and the AGND1 and AGND2 pins. Leaving the THR pin open results in a false detection of a <0°C battery temperature, and charging is disabled.

The ADP5360 charger monitors the voltage on the THR pin and suspends charging if the voltage is less than 0°C or higher than 60°C. For temperatures greater than 0°C and for temperatures lower than 60°C, the THR\_STATUS register is set accordingly.

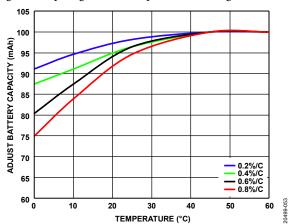

#### JEITA Li-Ion Battery Temperature Charging Specification

The charge of the ADP5360 is compliant with the JEITA Li-Ion battery charging temperature specifications as shown in Table 13.

The JEITA function can be enabled via the I<sup>2</sup>C interface. When the ADP5360 detects a JEITA cool condition, the charging current is reduced as shown in Table 14.

When the ADP5360 identifies a hot or cold battery condition, the battery isolation FET turns off. The battery isolation FET in the ADP5360 is linear regulated at  $V_{\text{SYS\_REG}}$  and provides power for the system.

Table 13. JEITA Li-Ion Battery Charging Specification Defaults

| Parameter                        | Symbol                  | Conditions                                                                                                                            | Min | Max | Unit |

|----------------------------------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------|-----|-----|------|

| JEITA Cold Temperature Limits    | I <sub>JEITA_COLD</sub> | No battery charging occurs.                                                                                                           |     | 0   | °C   |

| JEITA Cool Temperature Limits    | IJEITA_COOL             | Battery charging occurs at approximately 50% or 10% of programmed level. See Table 14 for specific charging current reduction levels. | 0   | 10  | °C   |

| JEITA Typical Temperature Limits | I <sub>JEITA_TYP</sub>  | Normal battery charging occurs at default and programmed levels.                                                                      | 10  | 45  | °C   |

| JEITA Warm Temperature Limits    | I <sub>JEITA_WARM</sub> | Battery termination voltage (V <sub>TRM</sub> ) is reduced by 100 mV from programmed value.                                           | 45  | 60  | °C   |

| JEITA Hot Temperature Limits     | I <sub>JEITA_HOT</sub>  | No battery charging occurs.                                                                                                           | 60  |     | °C   |

**Table 14. JEITA Reduced Charge Current Levels**

| Table 14. JETTA Reduced Charge | JEITA Cool Temperature Limit—Reduc | ed Charge Current Levels |

|--------------------------------|------------------------------------|--------------------------|

|                                |                                    | ICHG JEITA (mA)          |

| ICHG[4:0] (mA)                 | ILIM_JEITA_COOL = 0                | ILIM_JEITA_COOL = 1      |

| 00000 = 10                     | 10                                 | 10                       |

| 00001 = 20                     | 10                                 | 10                       |

| 00010 = 30                     | 10                                 | 10                       |

| 00011 = 40                     | 20                                 | 10                       |

| 00100 = 50                     | 20                                 | 10                       |

| 00101 = 60                     | 30                                 | 10                       |

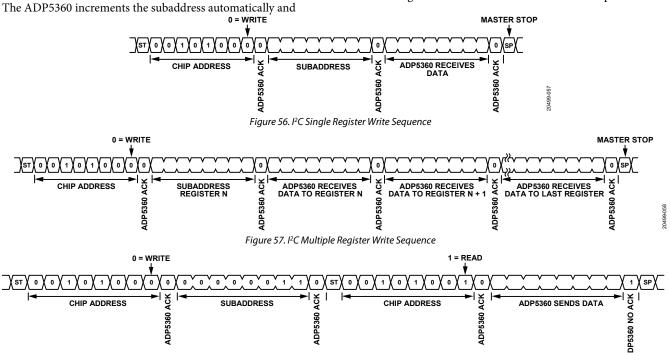

| 00110 = 70                     | 30                                 | 10                       |