Hi,

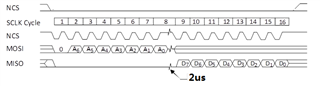

I'm facing an issue when communicating to a sensor using Nordic SPI master. The sensor requires nRF52832 to have 2us delay after first byte (address) is transmitted before receive byte (data) from the sensor. Is there any way to insert the 2us delay given Nordic's SPI Master has only continuous SPI clock input?

Here is my source code and I couldn't find a way to insert the 2us delay between the address and data. Any other workaround is appreciated as well. Thanks.

uint8_t spi_read ( uint8_t addr)

{

memset(m_rx_buf, 0, m_length); // Reset rx buffer and transfer done flag

spi_xfer_done = false;

nrf_drv_spi_transfer(&spi, &addr, 2, m_rx_buf, 2);

while (!spi_xfer_done)

{

__WFE();

}

return m_rx_buf[1];

}