Hi:

I have the following hardware structure:

FPGA < -- SPI -- > NRF5340 (TX) -- ! (ESB) ! -- NRF5340 (RX) < -- USB -- > PC

Due to the nature of my application, I need to send a lot of data through the ESB with high frequency. (250 bytes of data are transferred every 2ms.)

As a result, I've achieved what I needed. But the transfer was erratic, even when I put the two DK boards close together:

--> I control IO level flipping at SPI receive, ESB send, and ESB receive, respectively.

--> The results show that the ESB receives no more than 30s. And I need to reset PTX to have a high probability to work again.

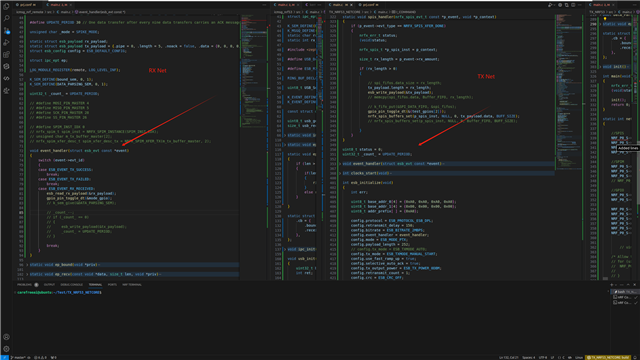

Here is my project with the code configuration:

PTX and PRX:

CONFIG_ESB_NEVER_DISABLE_TX=y

CONFIG_ESB_TX_FIFO_SIZE=64

CONFIG_ESB_RX_FIFO_SIZE=64

ret..delay = 150, ret...count = 1, tx_mode = manual_start, fast_ramp_up = true, auto_ack = true, crc = off

PTX:

spis_handler:

write_payload, toggle pin 1, set spis buffer

main:

start_tx, toggle pin 2

PRX:

esb_handler:

read_payload, toggle pin 3

The core code is as above, omitting some other code, but I don't think it will affect the solution of the problem, of course, if you need to provide other content or source code is ok.

For the transfer of data, I allow a small amount of data packet loss.

Thanks !