Hello DevZone,

One customer used Timer+PPI+GPIOTE to simulate an UART. Now it works fine.

However, when there is other timer's interrupt, the simulated UART may lose some bits.

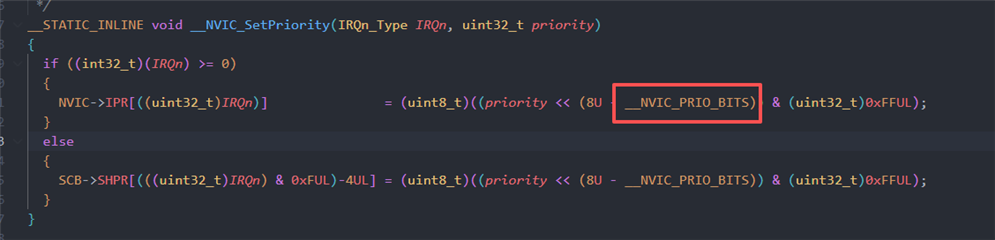

So we want to change the NVIC priority group.

Since there is no NVIC description in datasheet, we have to read the SDK initialization code. Now we know that in `SystemInit()` it don't set SCB->AIRCR or call `NVIC_SetPriorityGrouping()`.

We want to know if we can set the NVIC Priority Group in `nrf9160/ns`.

If we can, does this affect the interaction with modem?

Best regards,

Jayant