Hello,

We use the nrfx spis driver for communication between a ST processor (master) and a Fanstel BT840 module (nRF52840).

We have upgraded ncs from 2.6.0 to 3.2.1 and ran into a problem. The nRF52840 must now have a debugger (RTT) connected for the SPI slave to run. There does not need to go any messages over the RTT, it only needs connection.

Problem seems same as https://devzone.nordicsemi.com/f/nordic-q-a/126835/nrf54l15-spis-needs-constlat, except for it does not help to enable constlat.

When failure is present, the spis_handler() is not called anymore.

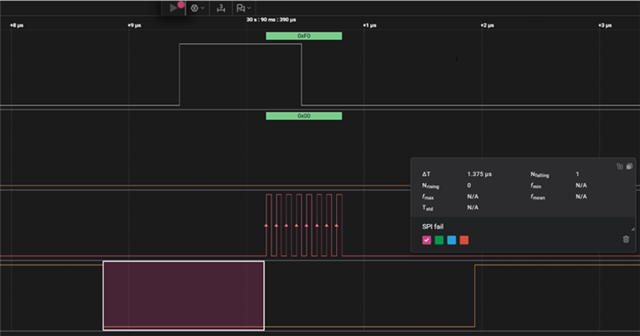

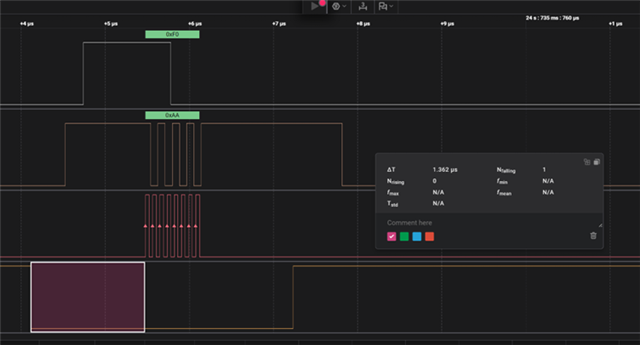

If we add a delay between SPI CS and first clock pulse, the SPI slave works.

Currently it seems like a delay of about 18uS works, while 2uS fails.

We also observes other strange things:

- Bootloader (mcuboot) from ncs 2.6.0 makes the SPI slave works (as will happen if we do a FOTA from old ncs 2.6.0 based firmware to new 3.2.1 based firmware). After FOTA to new firmware SPI slave works. But not if we update from 3.2.1 to 3.2.1.

Is there any explanation for what is happening here?

Any other workaround than delay between CS and first clock pulse?

Regards, Jan