Hello,

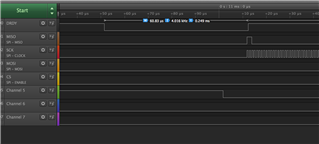

I am using nRF52 with ADS1292, and i am trying to sample at 8kHz with data throughput of 72kB/s, but some data is being randomly shifted giving me random spikes. This occurs on all available clock speeds to some degree. I am using Easy DMA. I am not getting any warnings or errors from the SPI driver as far as I can tell.

This issue does not occur at a lower data rate. Does this have something to do with overhead from the nRF SPIM drivers? I am also using I2C and other resources, but this also occurs with those additional resources disabled.

I'm trying to figure out what the limitation here is; is there a known limit on how many times you can call 'nrf_drv_spi_transfer' every second?

Thanks,