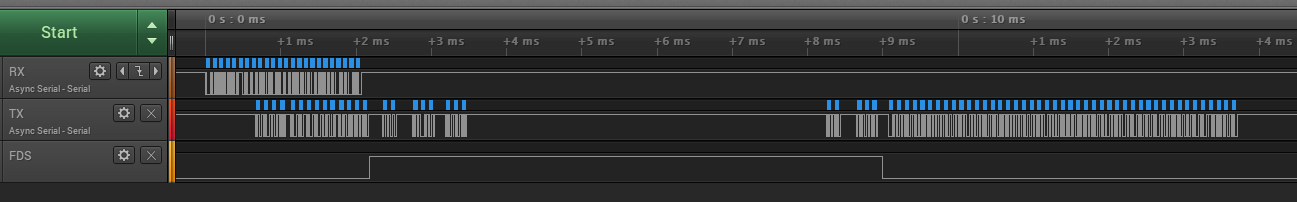

I've noticed that if I have data queued to go out over the uart (using app_uart_fifo) if I do an fds_record_update the UART TX is effected. You can see what's happening in the logic analyzer screenshot below. The FDS line goes high when fds_record_update is called and low once the FDS_EVT_UPDATE event is received.

Is this just to be expected since FDS seems to have higher priority or is there something I can do to improve this?