Hi,

Can someone help me with question on SPI?

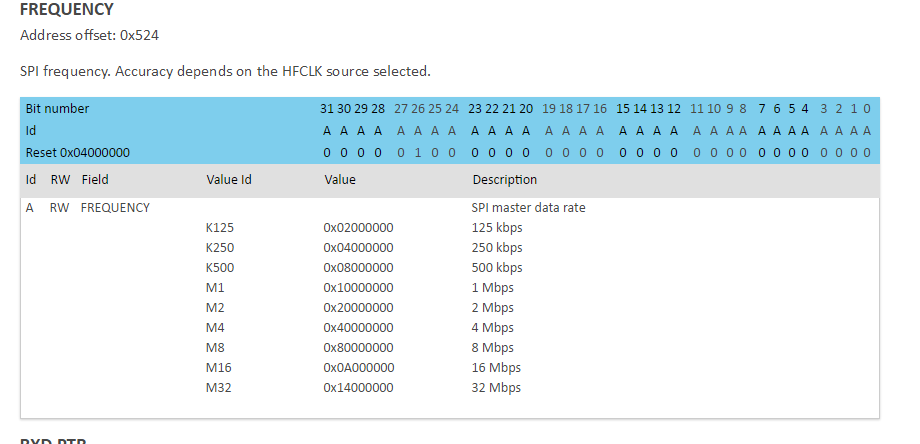

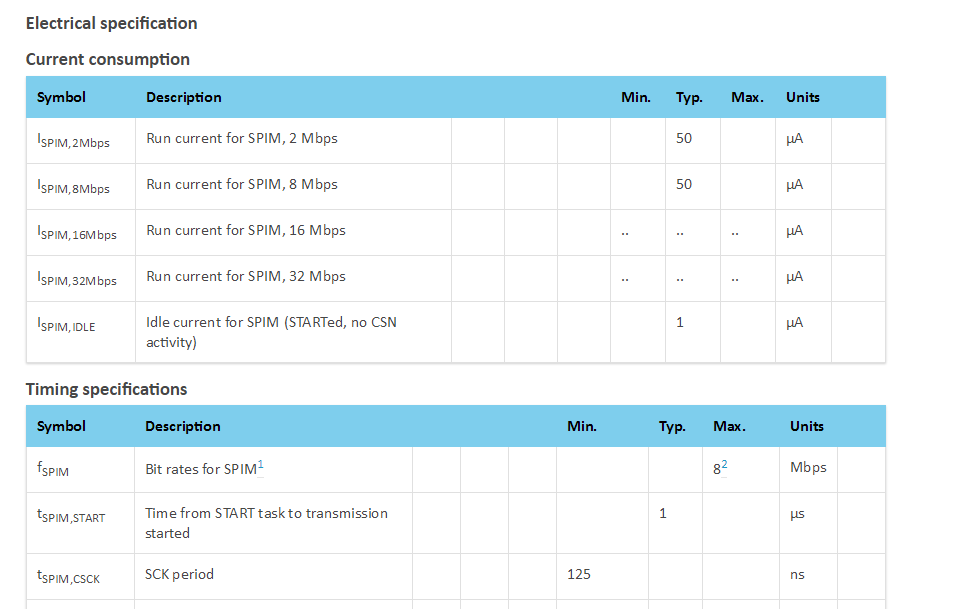

What is the difference between SPIM and SPI? They seem to have different clocks Also in the SPIM section, the frequency is said to be 32MHz in a number of places but then in one table again it is listed as 8Mbps. (which might be a typo) what do you make of this?