Hi,

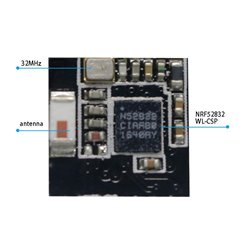

I'm working on this module. (https://fccid.io/2ALGYNRF52832AA/User-Manual/15-NRF52832AA-UserMan-r1-3763863)

This module has 1 cyristal bu nrf52 dk has 2 cyristal. Should i change something on software?

Hi,

I'm working on this module. (https://fccid.io/2ALGYNRF52832AA/User-Manual/15-NRF52832AA-UserMan-r1-3763863)

This module has 1 cyristal bu nrf52 dk has 2 cyristal. Should i change something on software?

*** Using Compiler 'V5.06 update 6 (build 750)', folder: 'C:\Keil_v5\ARM\ARMCC\Bin'

Build target 'nrf52832_xxaa'

compiling utf.c...

compiling bsp.c...

compiling boards.c...

compiling ble_advdata.c...

compiling ble_advertising.c...

compiling ble_conn_params.c...

compiling bsp_btn_ble.c...

compiling main.c...

compiling ble_srv_common.c...

compiling ble_nus.c...

compiling ble_link_ctx_manager.c...

compiling nrf_ble_gatt.c...

compiling ble_conn_state.c...

compiling nrf_ble_qwr.c...

compiling nrf_drv_clock.c...

compiling nrfx_power_clock.c...

compiling nrfx_prs.c...

compiling nrf_drv_uart.c...

compiling nrfx_clock.c...

compiling nrfx_uarte.c...

compiling nrfx_gpiote.c...

compiling nrfx_uart.c...

compiling app_error.c...

compiling app_fifo.c...

compiling app_error_handler_keil.c...

compiling app_scheduler.c...

compiling app_error_weak.c...

compiling app_button.c...

compiling app_timer.c...

compiling app_util_platform.c...

compiling hardfault_implementation.c...

compiling nrf_assert.c...

compiling app_uart_fifo.c...

compiling nrf_atfifo.c...

compiling nrf_atomic.c...

compiling nrf_atflags.c...

compiling nrf_balloc.c...

compiling nrf_fprintf.c...

compiling nrf_fprintf_format.c...

compiling nrf_memobj.c...

compiling nrf_strerror.c...

compiling nrf_section_iter.c...

compiling nrf_ringbuf.c...

compiling retarget.c...

compiling nrf_log_backend_rtt.c...

compiling nrf_pwr_mgmt.c...

compiling SEGGER_RTT_Syscalls_KEIL.c...

compiling nrf_log_backend_serial.c...

compiling nrf_log_default_backends.c...

compiling nrf_log_str_formatter.c...

compiling SEGGER_RTT.c...

compiling nrf_log_frontend.c...

assembling arm_startup_nrf52.s...

compiling SEGGER_RTT_printf.c...

compiling nrf_sdh_soc.c...

compiling system_nrf52.c...

compiling nrf_sdh.c...

compiling nrf_sdh_ble.c...

linking...

Program Size: Code=23284 RO-data=3384 RW-data=304 ZI-data=5992

FromELF: creating hex file...

".\_build\nrf52832_xxaa.axf" - 0 Error(s), 0 Warning(s).

Build Time Elapsed: 00:00:24

Set JLink Project File to "C:\Users\acer\Desktop\nRF5_SDK_15.2.0_9412b96\examples\ble_peripheral\ble_app_uart\pca10040\s112\arm5_no_packs\JLinkSettings.ini"

* JLink Info: Device "NRF52832_XXAA" selected.

JLink info:

------------

DLL: V6.32i, compiled Jul 24 2018 15:19:55

Firmware: J-Link ARM-OB STM32 compiled Aug 22 2012 19:52:04

Hardware: V7.00

S/N : 20090928

Feature(s) : RDI,FlashDL,FlashBP,JFlash,GDBFull

* JLink Info: Found SW-DP with ID 0x2BA01477

* JLink Info: Found SW-DP with ID 0x2BA01477

* JLink Info: Scanning AP map to find all available APs

* JLink Info: AP[2]: Stopped AP scan as end of AP map has been reached

* JLink Info: AP[0]: AHB-AP (IDR: 0x24770011)

* JLink Info: AP[1]: JTAG-AP (IDR: 0x02880000)

* JLink Info: Iterating through AP map to find AHB-AP to use

* JLink Info: AP[0]: Core found

* JLink Info: AP[0]: AHB-AP ROM base: 0xE00FF000

* JLink Info: CPUID register: 0x410FC241. Implementer code: 0x41 (ARM)

* JLink Info: Found Cortex-M4 r0p1, Little endian.

* JLink Info: FPUnit: 6 code (BP) slots and 2 literal slots

* JLink Info: CoreSight components:

* JLink Info: ROMTbl[0] @ E00FF000

* JLink Info: ROMTbl[0][0]: E000E000, CID: B105E00D, PID: 000BB00C SCS-M7

* JLink Info: ROMTbl[0][1]: E0001000, CID: B105E00D, PID: 003BB002 DWT

* JLink Info: ROMTbl[0][2]: E0002000, CID: B105E00D, PID: 002BB003 FPB

* JLink Info: ROMTbl[0][3]: E0000000, CID: B105E00D, PID: 003BB001 ITM

* JLink Info: ROMTbl[0][4]: E0040000, CID: B105900D, PID: 000BB9A1 TPIU

* JLink Info: ROMTbl[0][5]: E0041000, CID: B105900D, PID: 000BB925 ETM

ROMTableAddr = 0xE00FF000

* JLink Info: Reset: Halt core after reset via DEMCR.VC_CORERESET.

* JLink Info: Reset: Reset device via AIRCR.SYSRESETREQ.

Target info:

------------

Device: nRF52832_xxAA

VTarget = 3.300V

State of Pins:

TCK: 0, TDI: 0, TDO: 1, TMS: 0, TRES: 1, TRST: 1

Hardware-Breakpoints: 6

Software-Breakpoints: 8192

Watchpoints: 4

JTAG speed: 4000 kHz

Full Chip Erase Done.

Flash Erase finished 16:43:12

Load "C:\\Users\\acer\\Desktop\\nRF5_SDK_15.2.0_9412b96\\examples\\ble_peripheral\\ble_app_uart\\pca10040\\s112\\arm5_no_packs\\_build\\nrf52832_xxaa.axf"

Set JLink Project File to "C:\Users\acer\Desktop\nRF5_SDK_15.2.0_9412b96\examples\ble_peripheral\ble_app_uart\pca10040\s112\arm5_no_packs\JLinkSettings.ini"

* JLink Info: Device "NRF52832_XXAA" selected.

JLink info:

------------

DLL: V6.32i, compiled Jul 24 2018 15:19:55

Firmware: J-Link ARM-OB STM32 compiled Aug 22 2012 19:52:04

Hardware: V7.00

S/N : 20090928

Feature(s) : RDI,FlashDL,FlashBP,JFlash,GDBFull

* JLink Info: Found SW-DP with ID 0x2BA01477

* JLink Info: Found SW-DP with ID 0x2BA01477

* JLink Info: Scanning AP map to find all available APs

* JLink Info: AP[2]: Stopped AP scan as end of AP map has been reached

* JLink Info: AP[0]: AHB-AP (IDR: 0x24770011)

* JLink Info: AP[1]: JTAG-AP (IDR: 0x02880000)

* JLink Info: Iterating through AP map to find AHB-AP to use

* JLink Info: AP[0]: Core found

* JLink Info: AP[0]: AHB-AP ROM base: 0xE00FF000

* JLink Info: CPUID register: 0x410FC241. Implementer code: 0x41 (ARM)

* JLink Info: Found Cortex-M4 r0p1, Little endian.

* JLink Info: FPUnit: 6 code (BP) slots and 2 literal slots

* JLink Info: CoreSight components:

* JLink Info: ROMTbl[0] @ E00FF000

* JLink Info: ROMTbl[0][0]: E000E000, CID: B105E00D, PID: 000BB00C SCS-M7

* JLink Info: ROMTbl[0][1]: E0001000, CID: B105E00D, PID: 003BB002 DWT

* JLink Info: ROMTbl[0][2]: E0002000, CID: B105E00D, PID: 002BB003 FPB

* JLink Info: ROMTbl[0][3]: E0000000, CID: B105E00D, PID: 003BB001 ITM

* JLink Info: ROMTbl[0][4]: E0040000, CID: B105900D, PID: 000BB9A1 TPIU

* JLink Info: ROMTbl[0][5]: E0041000, CID: B105900D, PID: 000BB925 ETM

ROMTableAddr = 0xE00FF000

* JLink Info: Reset: Halt core after reset via DEMCR.VC_CORERESET.

* JLink Info: Reset: Reset device via AIRCR.SYSRESETREQ.

Target info:

------------

Device: nRF52832_xxAA

VTarget = 3.300V

State of Pins:

TCK: 0, TDI: 0, TDO: 1, TMS: 0, TRES: 1, TRST: 1

Hardware-Breakpoints: 6

Software-Breakpoints: 8192

Watchpoints: 4

JTAG speed: 4000 kHz

Erase Failed!

Error: Flash Download failed - "Cortex-M4"

Flash Load finished at 16:43:18

Try to erase the flash, flash the S112 or S132 SoftDevice(depending on what project you use), and then try flash the application from Keil again.

Use nRF Connect for Desktop and the Programmer app, or nrfjprog command line directly to flash the chip.

PS: For nRF52832 I would recommend that you use the S132 SoftDevice instead. For ble_app_uart that would be the Keil project in SDK_15_2_folder\examples\ble_peripheral\ble_app_uart\pca10040\s132\arm5_no_packs

The S132 can be found in the folder SDK_15_2_folder\components\softdevice\s132\hex

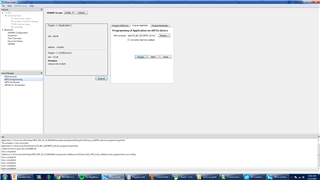

I fixed the problem. If i click the erase all button on NrfGo Studio i can upload the code successfully. Here is screenshots.

After this when i press the download button on keil program has uploaded successfully.

Programming Done.

Verify OK.

* JLink Info: Reset: Halt core after reset via DEMCR.VC_CORERESET.

* JLink Info: Reset: Reset device via AIRCR.SYSRESETREQ.

Application running ...

Flash Load finished at 10:17:44

But i still cant broadcasting. Here is my sdk_config.h clock configs.

// <h> Clock - SoftDevice clock configuration //========================================================== // <o> NRF_SDH_CLOCK_LF_SRC - SoftDevice clock source. // <0=> NRF_CLOCK_LF_SRC_RC // <1=> NRF_CLOCK_LF_SRC_XTAL // <2=> NRF_CLOCK_LF_SRC_SYNTH #ifndef NRF_SDH_CLOCK_LF_SRC #define NRF_SDH_CLOCK_LF_SRC 0 #endif // <o> NRF_SDH_CLOCK_LF_RC_CTIV - SoftDevice calibration timer interval. #ifndef NRF_SDH_CLOCK_LF_RC_CTIV #define NRF_SDH_CLOCK_LF_RC_CTIV 0 #endif // <o> NRF_SDH_CLOCK_LF_RC_TEMP_CTIV - SoftDevice calibration timer interval under constant temperature. // <i> How often (in number of calibration intervals) the RC oscillator shall be calibrated // <i> if the temperature has not changed. #ifndef NRF_SDH_CLOCK_LF_RC_TEMP_CTIV #define NRF_SDH_CLOCK_LF_RC_TEMP_CTIV 0 #endif // <o> NRF_SDH_CLOCK_LF_ACCURACY - External clock accuracy used in the LL to compute timing. // <0=> NRF_CLOCK_LF_ACCURACY_250_PPM // <1=> NRF_CLOCK_LF_ACCURACY_500_PPM // <2=> NRF_CLOCK_LF_ACCURACY_150_PPM // <3=> NRF_CLOCK_LF_ACCURACY_100_PPM // <4=> NRF_CLOCK_LF_ACCURACY_75_PPM // <5=> NRF_CLOCK_LF_ACCURACY_50_PPM // <6=> NRF_CLOCK_LF_ACCURACY_30_PPM // <7=> NRF_CLOCK_LF_ACCURACY_20_PPM // <8=> NRF_CLOCK_LF_ACCURACY_10_PPM // <9=> NRF_CLOCK_LF_ACCURACY_5_PPM // <10=> NRF_CLOCK_LF_ACCURACY_2_PPM // <11=> NRF_CLOCK_LF_ACCURACY_1_PPM #ifndef NRF_SDH_CLOCK_LF_ACCURACY #define NRF_SDH_CLOCK_LF_ACCURACY 7 #endif

What should i do?

Hi,

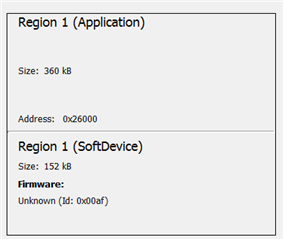

You will need to flash the SoftDevice. If you are using nRFGoStudio, go to the "Program SoftDevice" tab, and find the S132 SoftDevice in SDK_15_2_folder\components\softdevice\s132\hex , and flash it. After you have done that, it should look like this:

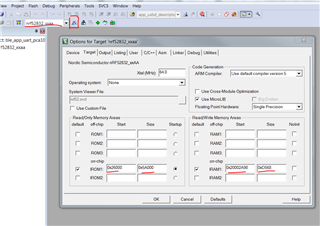

If you check the IROM/IRAM settings for your project, it should look like this:

Your sdk_config.h is not 100% correct, you need to have this also:

#define NRF_SDH_CLOCK_LF_RC_CTIV 16

#define NRF_SDH_CLOCK_LF_RC_TEMP_CTIV 2

#define NRF_SDH_CLOCK_LF_ACCURACY 1

It's working now!

Thanks a lot.