Hello

I'm using NRF52 PCA10040 board., SDK 15.2 libraries with GNU ARM GCC and Eclipse as an IDE developing FW on Windows10 x64.

I have been facing a problem trying to service external SPI flash memory (AT25SF041, but not only - you can read about it further). I'm not able to read memory ID registers. More precisely I got incorrect response from the memory.

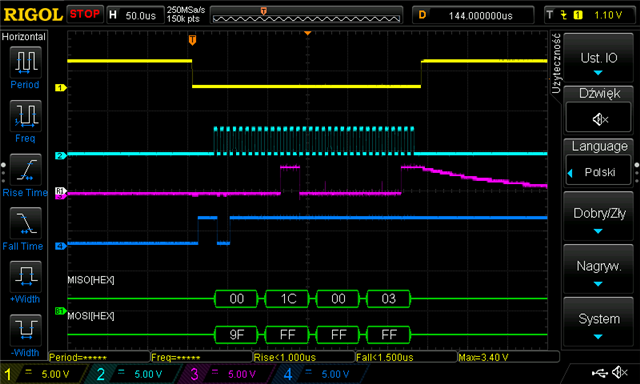

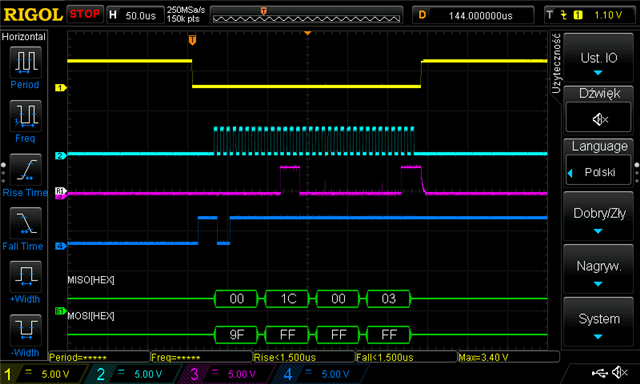

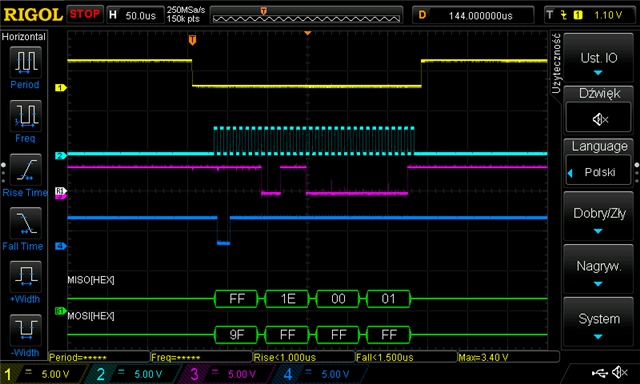

I was trying few memory chips from different vendors with the same result. I have no such a problem using STM32L0 MCU. What is more interesting, I have been investigating SPI communication at electric signal level using DSO and both communication (using NRF52 and STm32) looks exactly the same with the difference that memory responds to ID request got from SMT32 with appropriate device ID data but on NRF52 request it sends incorrect response.

Has anyone ever met such a strange problem?

Here is the low-level code I've written for AT25SF041 driver:

#include "nrf_gpio.h"

#include "nrfx_spi.h"

#include "logger.h"

#define CS_PIN 28

#define SCK_PIN 29

#define MISO_PIN 30

#define MOSI_PIN 31

static const nrfx_spi_t _xSpiHandler = NRFX_SPI_INSTANCE(0);

static nrfx_spi_config_t _xSpiConfig = NRFX_SPI_DEFAULT_CONFIG;

static uint8_t _bIsInitialized = 0;

static volatile uint8_t _bTransferFinished;

static void prvvSpiEventHandler(nrfx_spi_evt_t const* aEvent, void* aContext)

{

_bTransferFinished = 1;

}

void AT25SF041_vInitializeLL()

{

if (_bIsInitialized)

{

return;

}

/** Set SPI pins n the configuration object and initialize interface. */

_xSpiConfig.miso_pin = MISO_PIN;

_xSpiConfig.mosi_pin = MOSI_PIN;

_xSpiConfig.sck_pin = SCK_PIN;

_xSpiConfig.ss_pin = NRFX_SPI_PIN_NOT_USED;

_xSpiConfig.frequency = NRF_SPI_FREQ_125K ;

_xSpiConfig.mode = NRF_SPI_MODE_0;

nrfx_spi_init(&_xSpiHandler, &_xSpiConfig, &prvvSpiEventHandler, NULL);

/** Prepare CS pin and set its state to HGH. */

nrf_gpio_cfg_output(CS_PIN);

nrf_gpio_pin_set(CS_PIN);

_bIsInitialized = 1;

}

void AT25SF041_vSetCSActiveLL()

{

nrf_gpio_pin_clear(CS_PIN);

}

void AT25SF041_vSetCSInactiveLL()

{

nrf_gpio_pin_set(CS_PIN);

}

int8_t AT25SF041_bXferBytesLL(uint8_t* aTxBuf, uint8_t aTxLen, uint8_t* aRxBuf, uint8_t aRxLen)

{

nrfx_spi_xfer_desc_t xferDesc = NRFX_SPI_XFER_TRX(aTxBuf, aTxLen, aRxBuf, aRxLen);

AT25SF041_vSetCSActiveLL();

_bTransferFinished = 0;

nrfx_err_t error = nrfx_spi_xfer(&_xSpiHandler, &xferDesc, 0);

if (error != NRFX_SUCCESS)

{

return -1;

}

while (!_bTransferFinished)

{

}

AT25SF041_vSetCSInactiveLL();

return 0;

}