Hi,

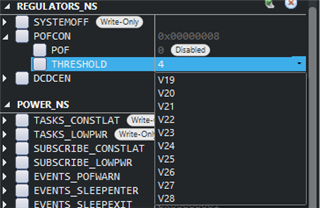

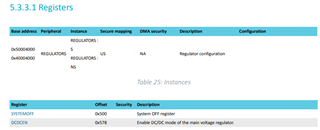

I was investigating the registers of the nrf9160 using segger embedded studio and found POFCON, which is not mentioned in the documentation.

Can you provide the documentation for this? Also, what is the best way to get access to the POFWARN interrupt? From what I see nrf_power_clock.c is using the interrupt for the clock without allowing access to the power interrupts?

Kind regards,

Thomas