hello,

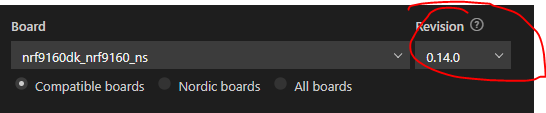

I tried to apply modifications to use and test the qspi flash mx25r6435f on the nrf9160dk development board. NCS version 2.2.0.

I can not see her.

prj

CONFIG_STDOUT_CONSOLE=y CONFIG_FLASH=y CONFIG_SPI=y CONFIG_SPI_NOR=y CONFIG_NORDIC_QSPI_NOR=y CONFIG_LOG=y CONFIG_SPI_LOG_LEVEL_ERR=y

overlay

&spi3 {

status = "okay";

cs-gpios = <&gpio0 25 GPIO_ACTIVE_LOW>;

pinctrl-0 = <&spi3_default>;

mx25r64: mx25r6435f@0 {

compatible = "jedec,spi-nor";

reg = <0>;

spi-max-frequency = <8000000>;

label = "MX25R64";

jedec-id = [ c2 28 17 ];

sfdp-bfp = [ e5 20 f1 ff ff ff ff 03 44 eb 08 6b 08 3b 04 bb ee ff ff ff ff ff 00 ff ff ff 00 ff 0c 20 0f 52 10 d8 00 ff 23 72 f5 00 82 ed 04 cc 44 83 68 44 30 b0 30 b0 f7 c4 d5 5c 00 be 29 ff f0 d0 ff ff ];

size = <67108864>;

has-dpd;

t-enter-dpd = <10000>;

t-exit-dpd = <35000>;

};

};

/{

aliases {

spiflash=&mx25r64;

};

};

main.c

/*

* Copyright (c) 2016 Intel Corporation.

*

* SPDX-License-Identifier: Apache-2.0

*/

#include <zephyr/kernel.h>

#include <zephyr/drivers/flash.h>

#include <zephyr/device.h>

#include <zephyr/devicetree.h>

#include <stdio.h>

#include <string.h>

#if defined(CONFIG_BOARD_ADAFRUIT_FEATHER_STM32F405)

#define SPI_FLASH_TEST_REGION_OFFSET 0xf000

#elif defined(CONFIG_BOARD_ARTY_A7_ARM_DESIGNSTART_M1) || \

defined(CONFIG_BOARD_ARTY_A7_ARM_DESIGNSTART_M3)

/* The FPGA bitstream is stored in the lower 536 sectors of the flash. */

#define SPI_FLASH_TEST_REGION_OFFSET \

DT_REG_SIZE(DT_NODE_BY_FIXED_PARTITION_LABEL(fpga_bitstream))

#elif defined(CONFIG_BOARD_NPCX9M6F_EVB) || \

defined(CONFIG_BOARD_NPCX7M6FB_EVB)

#define SPI_FLASH_TEST_REGION_OFFSET 0x7F000

#else

#define SPI_FLASH_TEST_REGION_OFFSET 0xff000

#endif

#define SPI_FLASH_SECTOR_SIZE 4096

const struct device *flash_dev;

void main(void)

{

const uint8_t expected[] = {0x55, 0xaa, 0x66, 0x99};

const size_t len = sizeof(expected);

uint8_t buf[sizeof(expected)];

int rc;

flash_dev = DEVICE_DT_GET(DT_ALIAS(spiflash));

if (!device_is_ready(flash_dev))

{

printk("%s: device not ready.\n", flash_dev->name);

return;

}

printf("\n%s SPI flash testing\n", flash_dev->name);

printf("==========================\n");

/* Write protection needs to be disabled before each write or

* erase, since the flash component turns on write protection

* automatically after completion of write and erase

* operations.

*/

printf("\nTest 1: Flash erase\n");

/* Full flash erase if SPI_FLASH_TEST_REGION_OFFSET = 0 and

* SPI_FLASH_SECTOR_SIZE = flash size

*/

rc = flash_erase(flash_dev, SPI_FLASH_TEST_REGION_OFFSET,

SPI_FLASH_SECTOR_SIZE);

if (rc != 0)

{

printf("Flash erase failed! %d\n", rc);

}

else

{

printf("Flash erase succeeded!\n");

}

printf("\nTest 2: Flash write\n");

printf("Attempting to write %zu bytes\n", len);

rc = flash_write(flash_dev, SPI_FLASH_TEST_REGION_OFFSET, expected, len);

if (rc != 0)

{

printf("Flash write failed! %d\n", rc);

return;

}

memset(buf, 0, len);

rc = flash_read(flash_dev, SPI_FLASH_TEST_REGION_OFFSET, buf, len);

if (rc != 0)

{

printf("Flash read failed! %d\n", rc);

return;

}

if (memcmp(expected, buf, len) == 0)

{

printf("Data read matches data written. Good!!\n");

}

else

{

const uint8_t *wp = expected;

const uint8_t *rp = buf;

const uint8_t *rpe = rp + len;

printf("Data read does not match data written!!\n");

while (rp < rpe)

{

printf("%08x wrote %02x read %02x %s\n",

(uint32_t)(SPI_FLASH_TEST_REGION_OFFSET + (rp - buf)),

*wp, *rp, (*rp == *wp) ? "match" : "MISMATCH");

++rp;

++wp;

}

}

}

any suggestions?

Thanks

babos