Hi, I am evaluating the nRF51822 for an ultra low power energy harvesting application.

I measured the time from power-on (VDD applied) to code exectution (GPIO toggle) using the PCA10005 Rev2.2.0 board from the nRF51822 development kit (Chip markings: N51822 QFAAGO 1404AS).

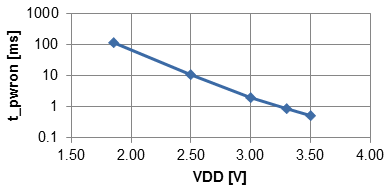

My results show that the startup time (t_pwron) increases from 0.85ms at VDD = 3.3V to over 100ms at VDD = 1.85V (See Figure below). In low voltage mode with VDD = 1.85V I get an even loger startup time of about 240ms. The VDD rise time in my setup is ca. 10us.

The problem is that the nRF51822 consumes about 500 uA during this startup time. The figure below shows a current measurement with a 10R shunt. I would like to lower VDD to save energy. However, because of the longer startup time, the nRF51822 actually consumes more energy for starting up with lower VDD.

My questions:

- why is the startup time loger with lower VDD?

- Can I do anything to reduce the startup time or the current consumption during startup?

Thank you for any suggestions.

I assume the nRF is held in Power On Reset (POR) during what I call t_pwron. However, the product specification v2.0 only gives minimal and typical t_POR times in Table 27 on page 38. Also, I can not find any specified VDD-dependency of t_POR in the product specification or reference manual.

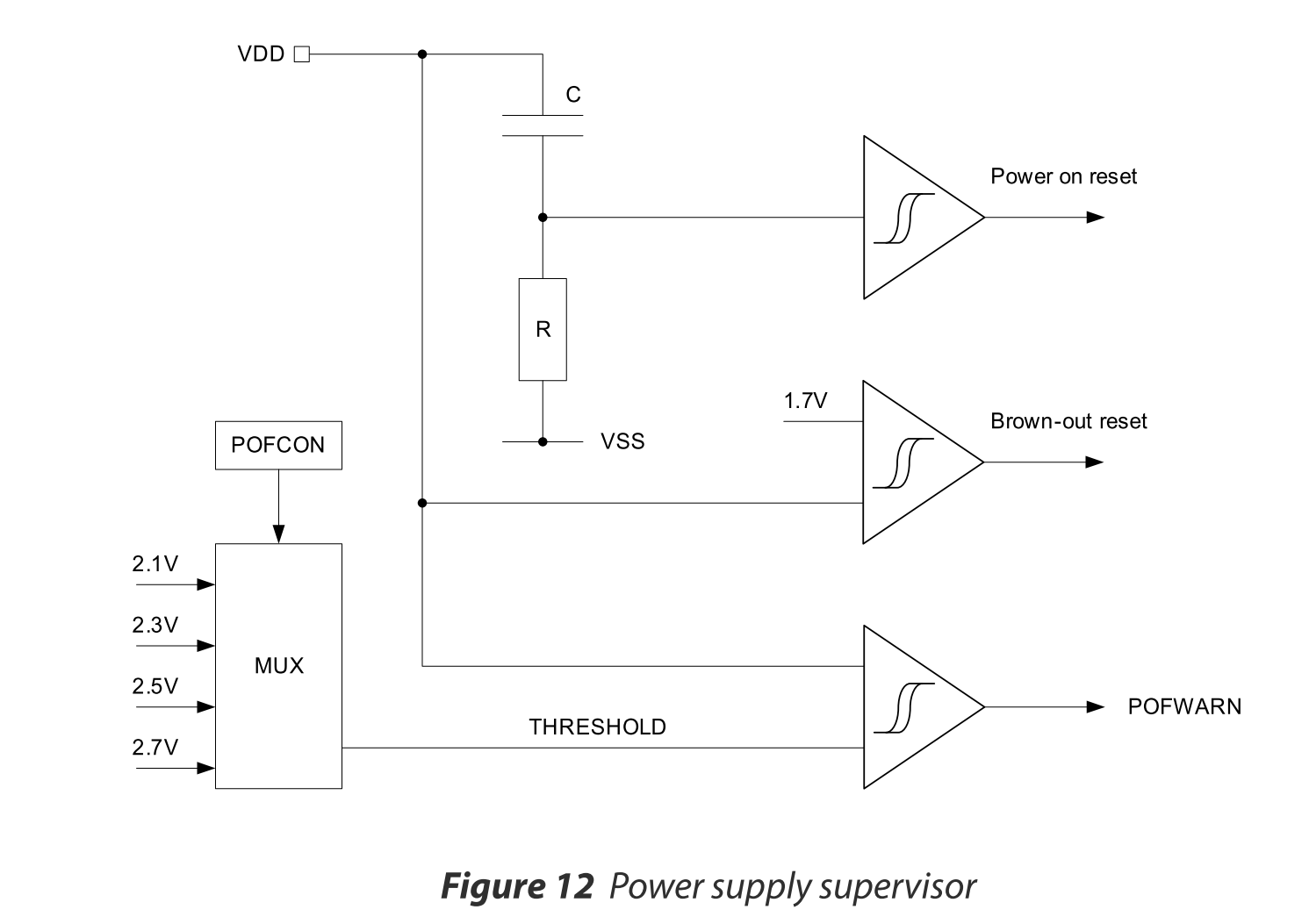

According to the POR-circuit shown in the reference manual (see Figure below), it makes sense that t_POR is longer for slower VDD rise times. However, I do not understand how to interpret the schematic regarding the VDD dependency of t_POR.