Hi All,

Project Information:

nrf52832

nRF5 SDK 17.1.0

Segger 5.70a

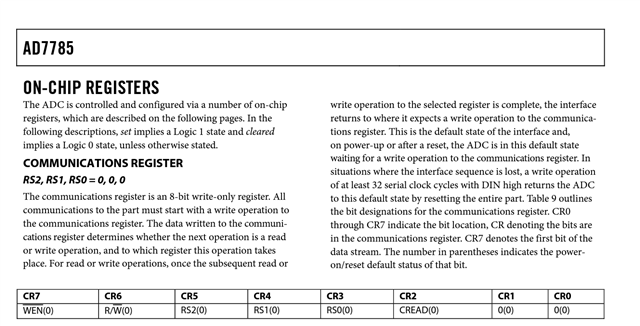

We have a custom board design that is using the Analog Devices AD7785 AFE to interface with strain gauges. The AFE uses SPI to communicate. According to the datasheet and an FAE, the AFE requires single byte SPI transactions in order to communicate and use the chip. I eventually found out about the errata for the nrf52832 that involves the SPIM driver not being capable of doing transfers that have the receive length set to 1. I have seen the suggested fix from the errata page here: Nordic Semiconductor Infocenter involving setup_workaround_for_ftpan_58(), but I'm not sure how to implement it properly.

The discussion and response with code example in this post Problems Implementing Workaround to get nrf52 to send an octet / one byte through SPI - Nordic Q&A - Nordic DevZone - Nordic DevZone (nordicsemi.com) seems to only cover how to transmit a single byte using SPI, which I have been able to accomplish by setting the rx_length in nrf_drv_spi_transfer() to 0. But I am looking to learn how to use setup_workaround_for_ftpan_58() to receive one byte as that is necessary to read data from the AFE according to the FAE.