I'm using Zephyr tool chain version 2.3.0. My chip is the nRF52832.

I'm writing two bytes out on the SPI bus. Byte[1] = 0X3b and Byte[0]=0x28

Here's what my spi_config looks like.

struct spi_cs_control spim_cs = {

.gpio = SPI_CS_GPIOS_DT_SPEC_GET(DT_NODELABEL(reg_my_spi_master)),

.delay = 0,

};

static const struct spi_config spi_cfg = {

.operation = SPI_WORD_SET(8) | SPI_TRANSFER_MSB |

SPI_MODE_CPOL | SPI_MODE_CPHA,

.frequency = 1000000,

.slave = 0,

.cs = &spim_cs,

};

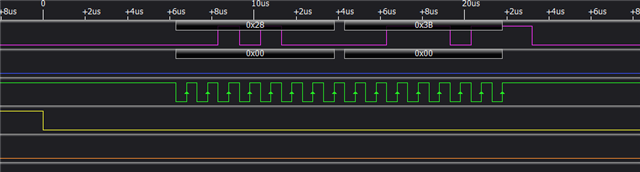

But the bytes are coming out swapped with byte[0] first and then byte[1]. Here it is on the logic analyzer.

How can I fix this so that the bytes come out most-significant first, the same way the bits come out? I believe this is what is expected of the SPI bus in its normal operation so that you can shift out multi-byte words without have to scramble and unscramble the bytes.

Regards,

Bret