Hi,

I am interfacing to this st accel+gyro, which i can successfully turn on with an nrf52 on and read back the device id using the nrf5 sdk, by using nrf_drv_spi_transfer.

I'm having trouble getting a response now im using nrf connect 2.4.1 and zephyrs spi_transceive which is generating the same clock, CS, and MOSI output signals as nrf_drv_spi_transfer previously. One difference i can see is the MOSI was high when no data was transmitted used on the nrf5 and would be low on the nrf connect. Using the connect sdk I've tried changing the drive strength to all variants by altering nordic,drive-mode in the &pinctrl for my .overlay file but still have no luck.

When i scope the miso on either it defaults to a value of 0x0C on both implementations, but with no scope on the line for the nrf5 i get correct returned values.

I should clarify, in the images below i'm sending 0x0F which is the who_am_i ID and its a read command so the first bit is high resulting in 0x8F which i get, and then 8 more clock cycles are given expecting a response on the MISO.

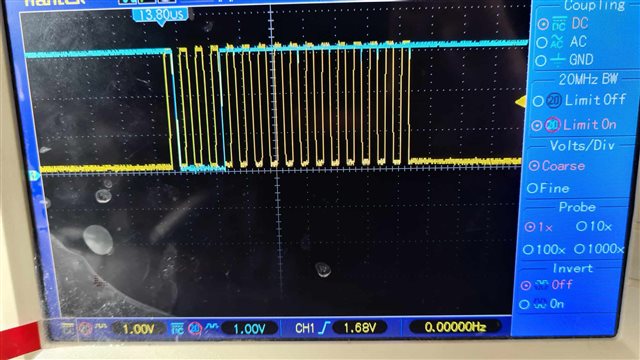

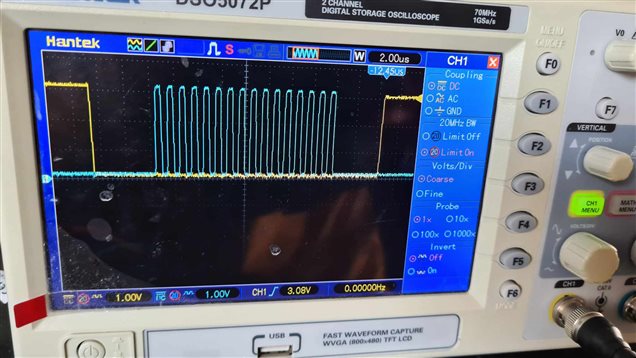

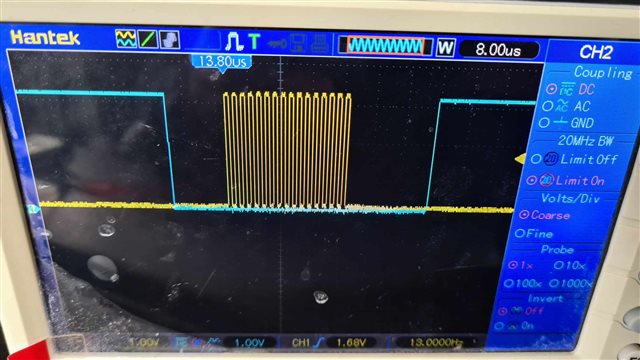

For reference here is the MOSI+ CLK, CS +CLK and MISO + CLK respectively for the nrf5 implementation:

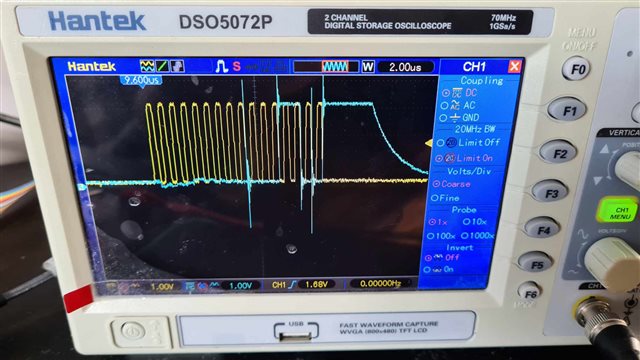

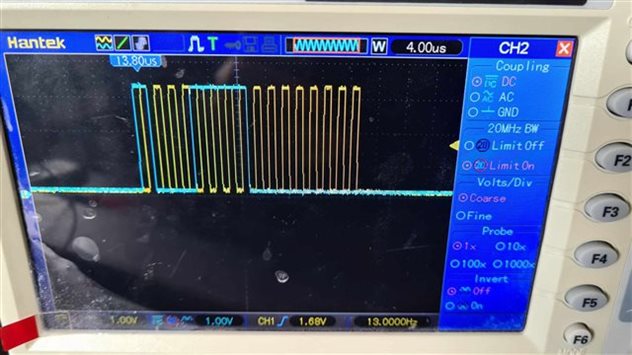

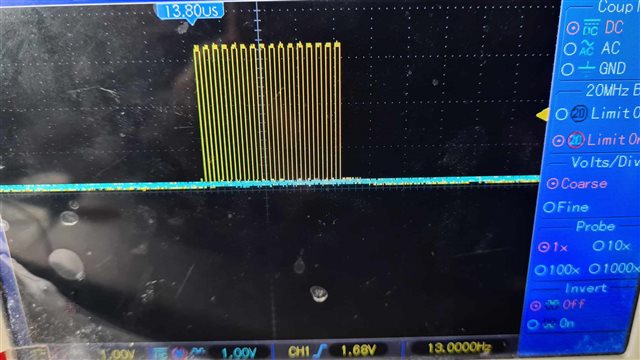

and here is the MOSI+ CLK, CS +CLK and MISO + CLK for the nrf connect 2.4.1 implementation:

I was wondering if there are any listed differences between the default settings for gpio configurations in the legacy driver and the new spim (i believe the zephyr spi driver is just a wrapper on top of spim)?.

Any help or comments would be greatly appreciated.

Kind regards,

Liam