Dear Support Team

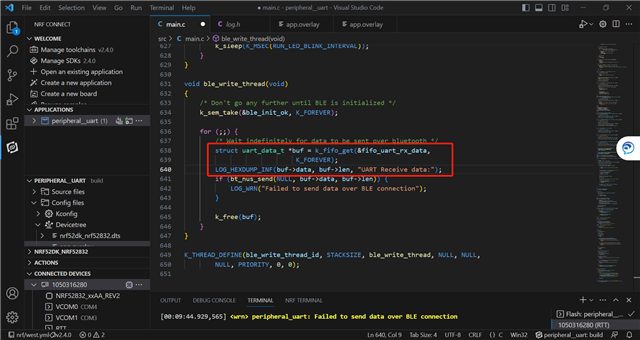

I test the peripheral_uart sample from NCS(V2.4.0), I found that the data got by calling the k_fifo_get() less than the data received by the UART RX. For example, I sent 208 Bytes to the UART RX but it just printed 200 Bytes by calling the LOG_HEXDUMP_INF() macro as the screenshots below showing, and UART baud rate I set is 921600.

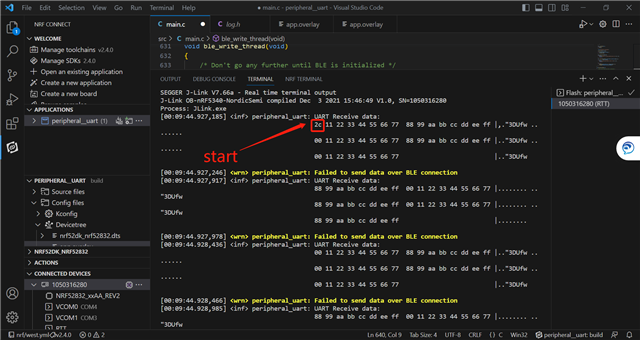

Below screenshot below shows I send 208 Bytes to the RX. This packet starts with 2c and ends with 2c.

![]()

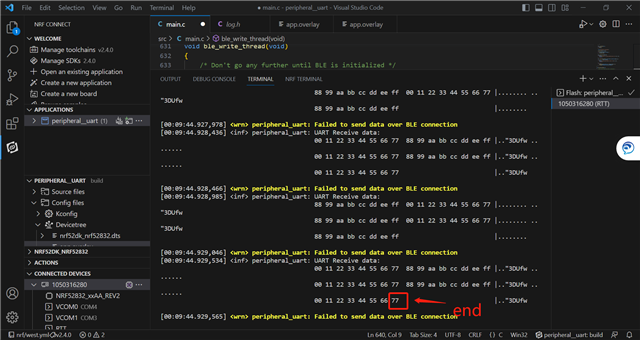

Below screenshot shows the data printed by calling the LOG_HEXDUMP_INF() macro. It starts with 2c but ends with 77, so there was still 8 bytes haven't been printed.

Why it would loss printing the 8 bytes? How could I print all of the any size of data packet without end with \r or \n received by the UART RX? Many thanks.