Hi,

I make a customer board and used GD25Q80C as the external Flash IC (not MX25);

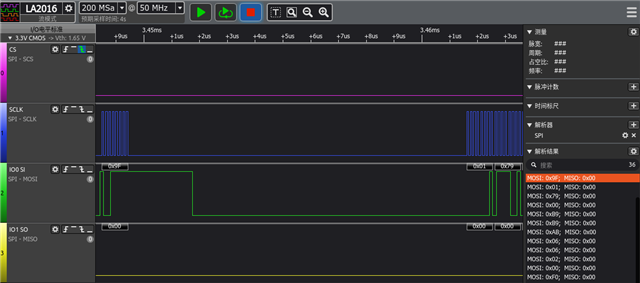

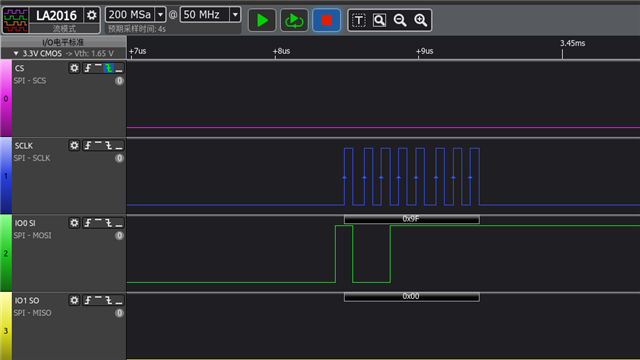

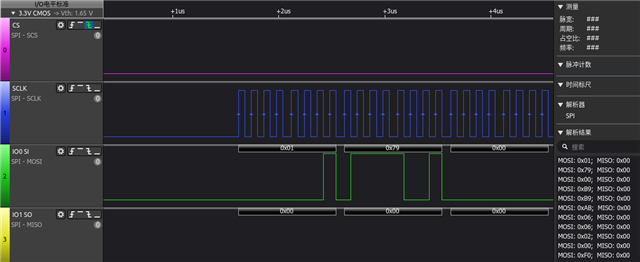

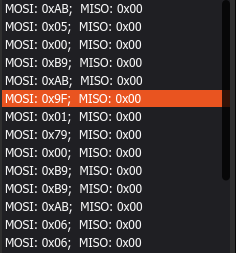

Read the sfdp bfp of Flash by jesd216 sample (zephyr \ samples \ drivers \ jesd216),But it failed and prompted "SFDP magic 000000 invalid";

However, when I replaced GD25Q80C with MX25R64, it was successful;

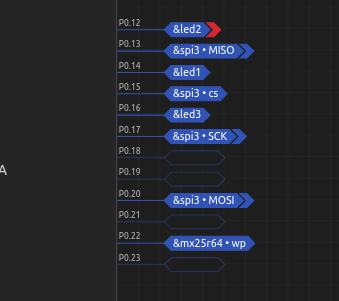

My configuration is as follows:

I basically haven't changed the configuration of samples, only the IO port has been modified;

Can you see what the problem is?

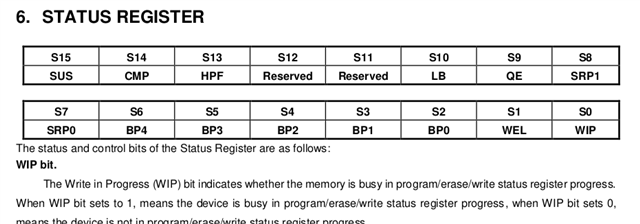

The specifications for this IC are as follows

&spi2 {

compatible = "nordic,nrf-spi";

status = "okay";

cs-gpios = <&gpio0 15 GPIO_ACTIVE_LOW>;

pinctrl-0 = <&spi2_default>;

pinctrl-1 = <&spi2_sleep>;

pinctrl-names = "default", "sleep";

mx25r64: mx25r6435f@0 {

compatible = "jedec,spi-nor";

reg = <0>;

spi-max-frequency = <8000000>;

jedec-id = [c8 40 14];

size = <8388608>;//67108864

wp-gpios = <&gpio0 22 GPIO_ACTIVE_LOW>;

hold-gpios = <&gpio0 24 GPIO_ACTIVE_LOW>;

};

};

spi2_default: spi2_default {

group1 {

psels = <NRF_PSEL(SPIM_SCK, 0, 17)>,//19

<NRF_PSEL(SPIM_MOSI, 0, 20)>,//20

<NRF_PSEL(SPIM_MISO, 0, 13)>;//21

};

};

spi2_sleep: spi2_sleep {

group1 {

psels = <NRF_PSEL(SPIM_SCK, 0, 17)>,//19

<NRF_PSEL(SPIM_MOSI, 0, 20)>,//20

<NRF_PSEL(SPIM_MISO, 0, 13)>;//21

low-power-enable;

};

};

/////prj

CONFIG_STDOUT_CONSOLE=y

CONFIG_FLASH=y

CONFIG_FLASH_JESD216_API=y

# Assume the standard SPI NOR flash driver. If the device uses

# another driver add an override configuration in boards/.

CONFIG_SPI=y

CONFIG_SPI_NOR=y

CONFIG_UART_CONSOLE=y

CONFIG_CLOCK_CONTROL_NRF_K32SRC_RC=y

CONFIG_SOC_ENABLE_LFXO=n