Setup:

NCS v.2.4.1

nRF52840DK

Hello, I am seeking guidance on safeguarding the nRF flash from power failures during writing or erasing. However, I am uncertain if I have correctly interpreted the specifications outlined in the documentation (https://infocenter.nordicsemi.com/pdf/nRF52840_PS_v1.7.pdf).

Quoting from the specification: "If the power failure warning is enabled, and the supply voltage is below the threshold, the power-fail comparator will prevent the NVMC from performing write operations to the flash."

I have enabled and set the threshold as follows:

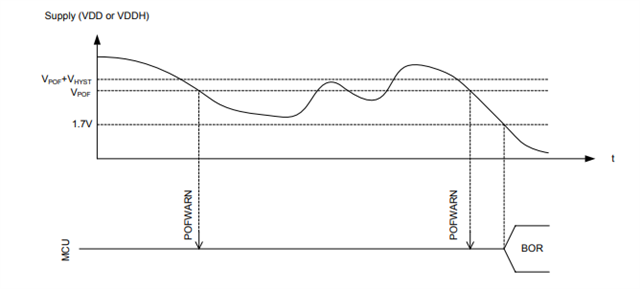

nrf_power_pofcon_set(NRF_POWER, true, NRF_POWER_POFTHR_V27);Based on the chart provided, my expectation is that when the VDD voltage drops below 2.7V, EVENTS_POFWARN will be generated and set until the voltage rises above 2.7V + Vhyst. Beyond that value, EVENTS_POFWARN will be cleared.

My questions are:

- Does the automatic clearing of EVENTS_POFWARN happen by the hardware itself?

- How is flash memory protected? Is the flash driver responsible for checking if the event is asserted, and if so, where can I find that check? Or does it happen automatically without any software action?

Additionally, I am contemplating the use of nrfx_power (specifically, nrfx_power_pof_init and nrfx_power_pof_enable) in conjunction with ERRATA 242 ("NVMC operations during POFWARN cause the CPU to hang"). I am concerned that the nrfx_power_irq_handler might clear EVENTS_POFWARN, which is checked by the suspend_pofwarn() function introduced by the errata. Since these two processes are not synchronized, there's a possibility that the event is cleared just before the check made by suspend_pofwarn(). Consequently, writing or erasing might be permitted even when it shouldn't be.