Hello,

I have developed an NCS/Zephyr-based application that is able to stream out .WAV files over the I2S peripheral.

I have a dev board using a MAX98357A audio amplifier. This amplifier is able to interpret the I2S output from my nRF52840 and it plays my .WAV file normally out of a speaker.

Here is the I2S configuration I'm using to configure the Zephyr I2S driver:

my_i2s_config.word_size = SAMPLE_BIT_WIDTH; // 16 my_i2s_config.channels = NUMBER_OF_CHANNELS; // 1 my_i2s_config.format = I2S_FMT_DATA_FORMAT_I2S; my_i2s_config.options = I2S_OPT_BIT_CLK_MASTER | I2S_OPT_FRAME_CLK_MASTER; my_i2s_config.frame_clk_freq = SAMPLE_FREQUENCY; // 16000 my_i2s_config.mem_slab = &mem_slab; my_i2s_config.block_size = BLOCK_SIZE; my_i2s_config.timeout = TIMEOUT;

With these settings, I am observing these I2S output clocks on my oscilloscope:

BCLK = 510kHz

LRCLK = 15.9kHz

BCLK to LRCLK Ratio: 32

Now, I want to integrate a more advanced audio amplifier: the TI TAS2563. However, this audio amplifier does not support BCLK to LRCLK ratio of 32. It requires a minimum ratio of 64.

I still want my audio sampling frequency to be 16kHz, so I need to increase the BCLK speed up to ~1.024MHz.

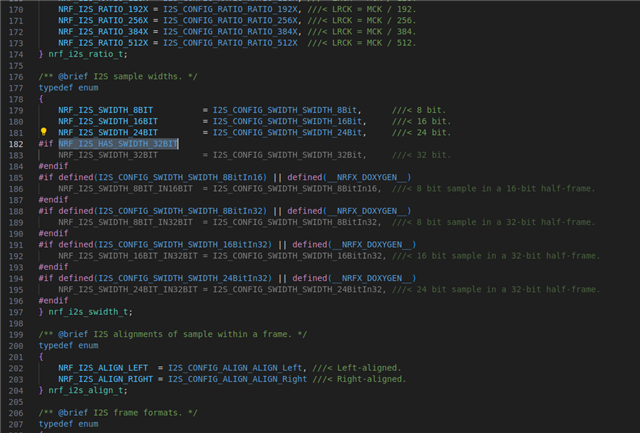

I know that the previous NRFX drivers had registers for configuring the MCK_SETUP and MCK/LRCK ratio. I had a previous project (before NCS/Zephyr) where we used a MCK_SETUP value of NRF_I2S_MCK_32MDIV21 and a ratio value of NRF_I2S_RATIO_96X to get 16kHz streaming working. If I'm remembering the math correctly, this would give:

32MHz / 21 = 1.524MHz I2S peripheral clock

1.524MHz / 96 BCLKs/LRCLK = 15.9kHz LRCLK (close enough for 16kHz sampling)

Unfortunately, I do not see the options in the Zephyr driver to achieve this level of configuration over the I2S peripheral.

Is there a way to configure the I2S peripheral from Zephyr such that I have a 16kHz LRCLK and a BCLK to LRCLK ratio of 64 or higher?