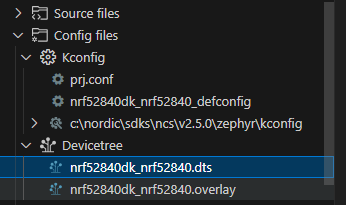

I am trying to set up two GPIOs to control an external chip. Development and testing is currently using the nRF5340 DK. NCS version is 2.5.0.

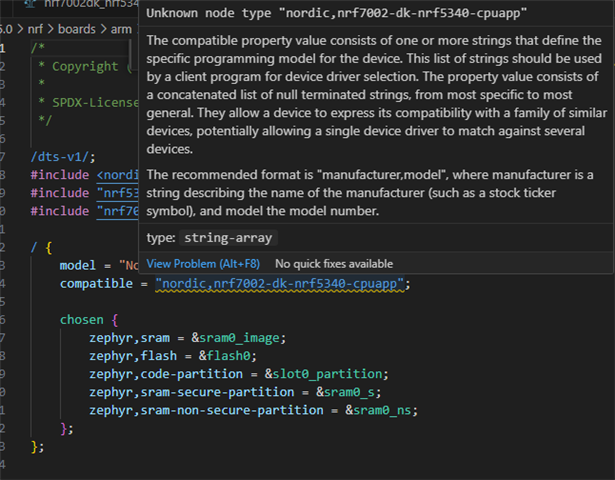

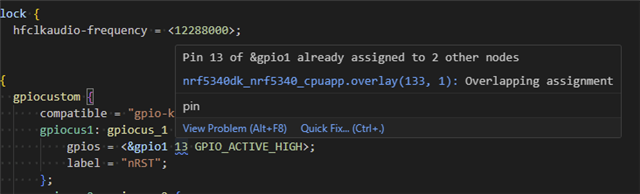

In my nrf5340dk_nrf5340_cpuapp.overfile, I have the following. There are other GPIOs, but ignore those for now. Also, ignore the fact that reset should be an open-drain. I am just sanity testing right now. The pins are not connected and only being monitored with a logic analyzer.

In the code we have:

and then to test it we have the following declarations

and test code

asd

The MFIO pin (P1.14) moves. The reset pin (P1.13) does not. I have done a lot of tracing to determine exactly where the problem is occurring. It happens at:

When the pin configuration gets changed from input-with-pullup to output. This is in nrf_gpio_reconfigure() and is occurring in the secure domain at 0x50842a34. The nRF Debug peripheral registers view does not seem to give access to GPIO P1 in the secure domain, so I am using gdb commands in the debug console to set and verify the P1_S registers and observing the result via Saleae logic analyzer. I must do this while still in the nrf driver functions or I lose privilage to access 0x50000000 register range from the debug console.

Here are my observations:

Set P1.13 high via pullup, *((uint32_t*)0x50842a34)=0xC, pin goes high.

Set P1.13 low via pulldown, *((uint32_t*)0x50842a34)=0x4, pin goes low.

Set P1.13 to output, *((uint32_t*)0x50842a34)=0x3, pin goes low and stays low regardless of state of P1->OUT bit 13. I have set and cleared the bit by using *((uint32_t*)0x50842808)=0x2000 and *(uint32_t*)0x5084280c)=0x2000. The pin state does not change. 0x50842a34 verifies that it is in output mode, owned by APP CPU, with drive set to S0S1 (i.e. register = 0x03). When I change P1.14 using *((uint32_t*)0x50842808)=0x4000 and *((uint32_t*)0x5084280c)=0x4000, that pin does change.

One thing I noticed, if I have the pin in input-with-pullup state and then set it to output, it doesn't go straight to 0. It decays to 0 as though it's draining through something (possibly the Saleae?). That's why I suggest that it seems the output driver is not even connected when PIN_CFG[13].DIR is set to output.

I have searched around in the nRF5340 product specification and on the PCA10095 schematic and cannot figure out anything that would be interfering with P1.13.