Hi,

For development using SDK17.1 and keil,Follow the examples in this document for development: Getting started with Nordic's Secure DFU bootloader, a step by step guide - Software Development Kit - nRF5 SDK guides - Nordic DevZone (nordicsemi.com)

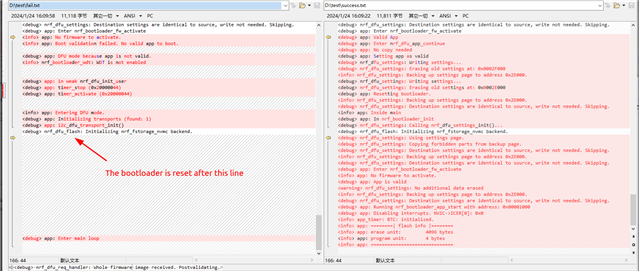

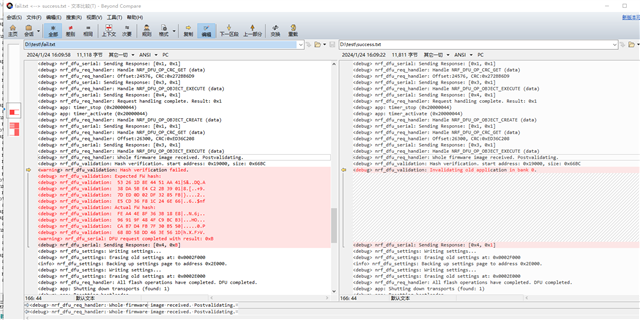

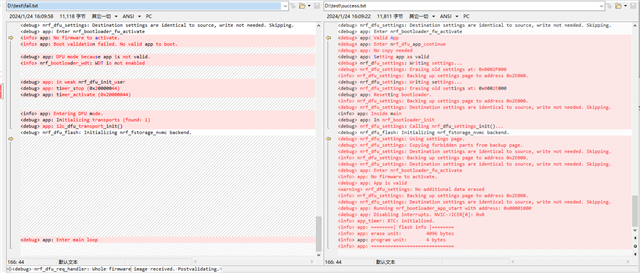

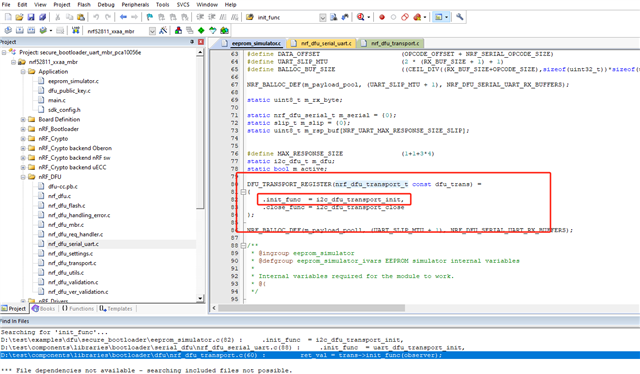

DFU (DFU-UART) is required. Due to project requirements, UART in bootloader is changed to IIC for DFU upgrade. A problem is that only the j-link RTT Viewer can successfully verify the HASH value.log Compare the following screenshot:

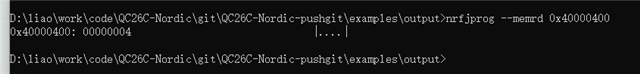

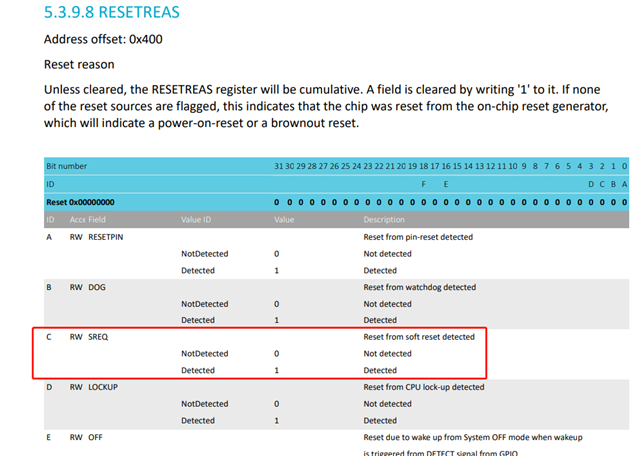

The current test outputs log information from the UART. j-link RTT Viewer selects Connection or no connection (If the chip is not connected, the HASH verification fails)

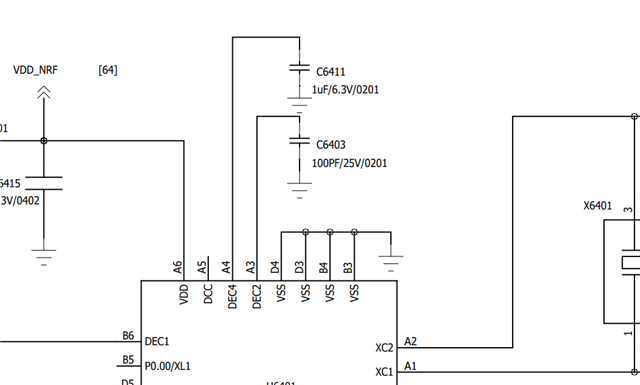

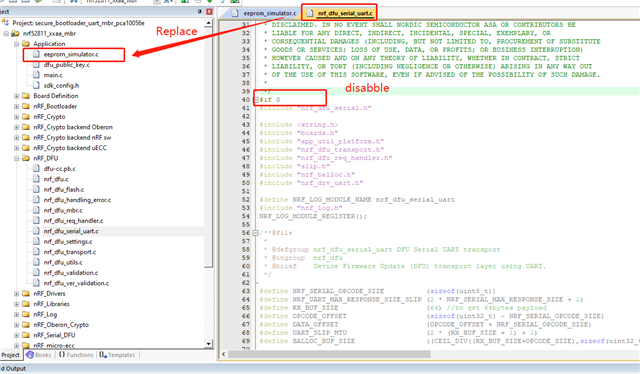

From UART to IIC, the following changes have been made:

Have been looking for a long time the cause of the problem, 52811_DFU.zip is the original program used for development.

Please take a look at the cause of this problem. Thank you very much!

Best regards

Stars