Hi,

I need to add SPI function to my project, according to this thread

RE: SPI example for nRF52833 with nRF Connect SDK 2.3.0

I download this async SPI example from github.

https://github.com/too1/ncs-spi-master-slave-example

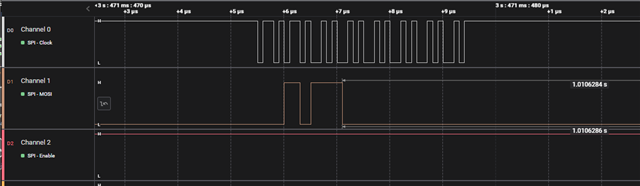

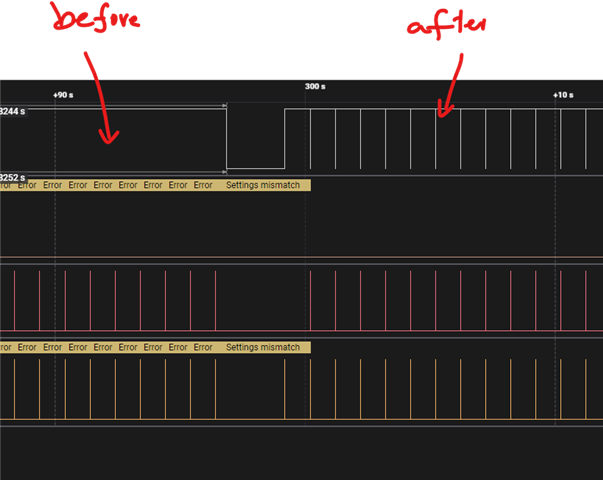

When I run it in ncs v2.5.1, nRF52DK. I get the following RTT log

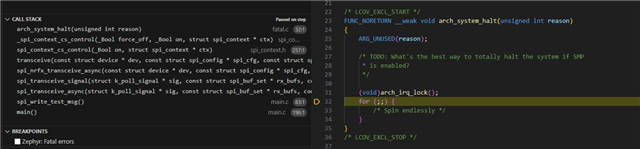

00> [00:00:00.425,720] <err> os: ***** Reserved Exception ( -16) ***** 00> [00:00:00.425,720] <err> os: r0/a1: 0x200020c0 r1/a2: 0x00002151 r2/a3: 0x0000759b 00> [00:00:00.425,750] <err> os: r3/a4: 0x00002125 r12/ip: 0x00002125 r14/lr: 0x00002125 00> [00:00:00.425,750] <err> os: xpsr: 0x00000000 00> [00:00:00.425,781] <err> os: Faulting instruction address (r15/pc): 0x00002125 00> [00:00:00.425,811] <err> os: >>> ZEPHYR FATAL ERROR 0: CPU exception on CPU 0 00> [00:00:00.425,842] <err> os: Current thread: 0x20000800 (main) 00> [00:00:01.240,417] <err> os: Halting system

and paused on spi_transceive_async()

Does spi_transceive_async() support in the ncs v2.5.1?

I attached my project file also, just add some configs for RTT log.