Dear Support Team

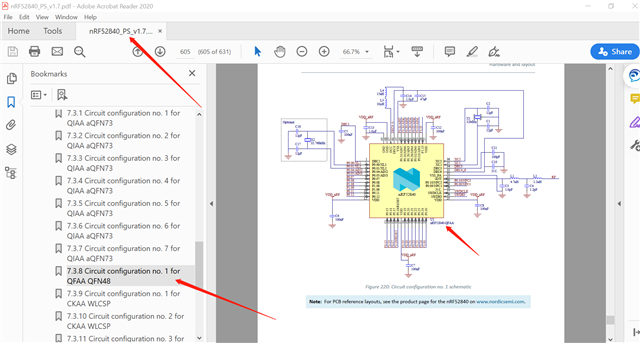

We use the nRF52840 QFAA QFN48 and the reference circuitry as the screenshot below for our board, but the board could not run after we programmed the hello_world or peripheral_uart sample into the chip.

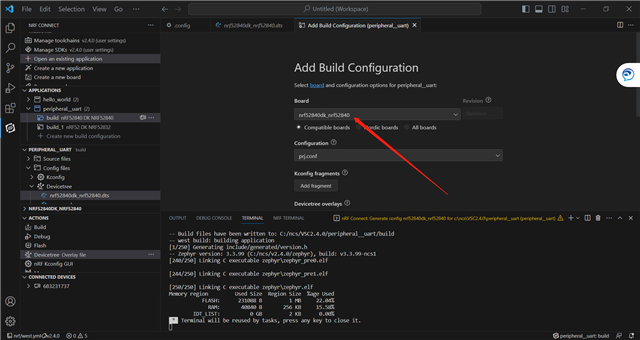

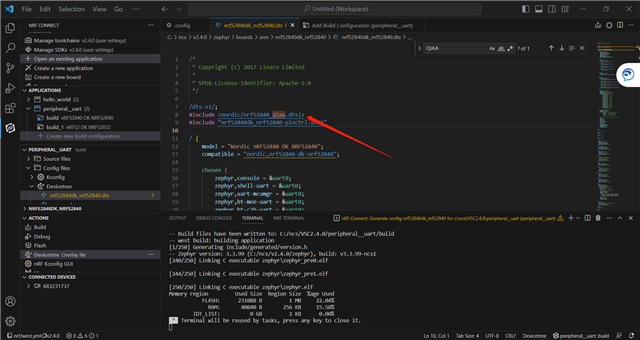

We found that the sample was configured for the nRF52840 QIAA by default after we selected the board of nrf52840dk_nrf52840 on the Add Build Configuration like the screenshot below.

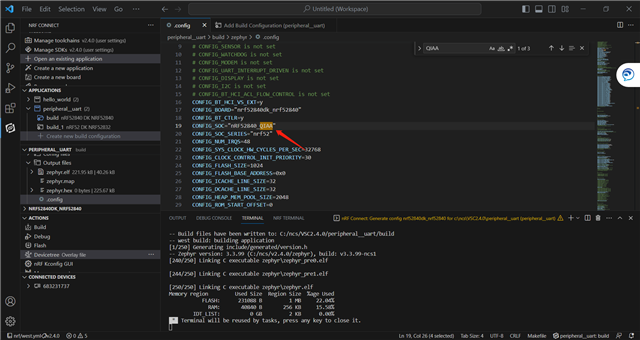

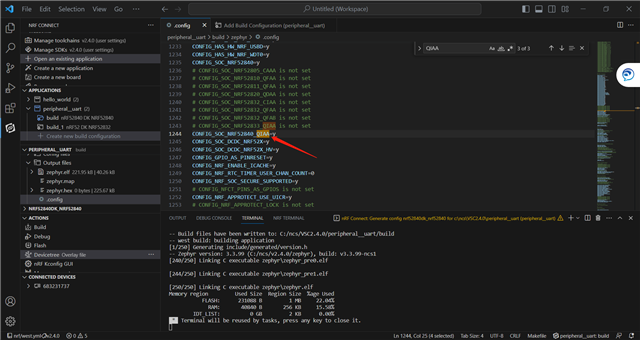

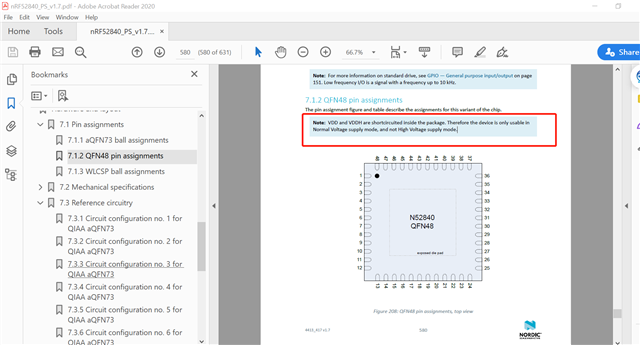

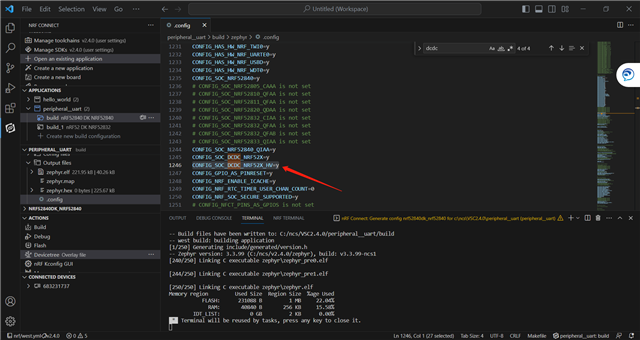

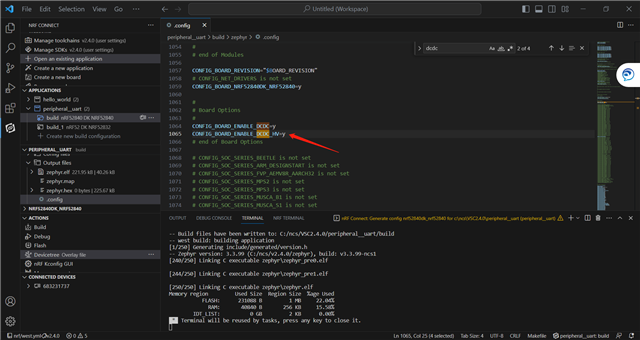

And we also found that VDD and VDDH are shortcircuited inside the package. Therefore the device is only usable in Normal Voltage supply mode, and not High Voltage supply mode., but the default configuration has the CONFIG_BOARD_ENABLE_DCDC_HV=y and the CONFIG_SOC_DCDC_NRF52X_HV=y in the .conf file like the screenshot below. We were not sure this is the reason of the chip could not run normal.

Is there anything specific configuration for the nRF52840 QFAA QFN48 in these samples? Many thanks.