Hi DevZone,

I'm a hobbyist working on a wearable project using nrf52840 and a memory LCD from sharp. I'm currently using the monochrome LS018B7DH02 and driving it using SPI (I believe this uses the SPIM peripheral with EasyDMA under the hood, but I'm not positive). This works great because the display only has one data line and one clock line (that is, it's a traditional SPI device), and I can buffer the data, feed it to the SPIM peripheral, and be done.

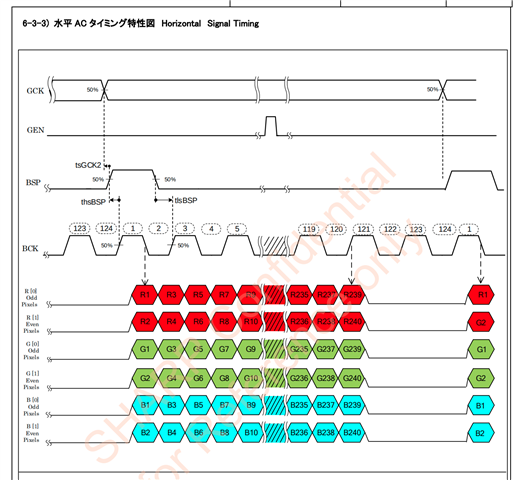

I'm considering moving my project to instead use the LS021B7DD02 (datasheet) memory LCD, which has 2-bit RGB color per pixel, but I'm not sure what the best way to do it is. Instead of one data line, this one has six - two each for red, green, and blue - in addition to a more complex series of clock signals. The relevant part of the timing diagram from the datasheet looks like this:

My question is this: what is the most power-efficient way to drive this LCD from the perspective of the nrf52840 CPU? Power efficiency in my mind seems like it should mostly be decided by how much CPU-on time the update uses, which is why I think I get such a benefit from the SPIM peripheral / EasyDMA under my current scheme. With six data lines, though, I'm not sure if there exists a peripheral (or a way to abuse a peripheral) to drive all of them in sync with the same clock from a memory buffer. The alternative is bit-banging the output with GPIO pins, which I'm sure would work, but would eat up a comparatively large amount of CPU time (moving from bitbanging to SPIM under my current one-channel scheme was a 4x speedup!) and thus consume more power.

Thanks!