Hi All,

My issue is may connected to

TWI HW producing shortened ACK clock pulse

I'm using:

- nRF52 DK dev. board

- nrf52dk_nrf52832_defconfig

//overlay

&i2c0 {

appi2c: appi2c@8 {

reg = <0x08>;

label = "APPI2C";

};

};

//compiled device tree

i2c0: arduino_i2c: i2c@40003000 {

compatible = "nordic,nrf-twi";

#address-cells = < 0x1 >;

#size-cells = < 0x0 >;

reg = < 0x40003000 0x1000 >;

clock-frequency = < 0x186a0 >;

interrupts = < 0x3 0x1 >;

easydma-maxcnt-bits = < 0x8 >;

status = "okay";

pinctrl-0 = < &i2c0_default >;

pinctrl-1 = < &i2c0_sleep >;

pinctrl-names = "default", "sleep";

appi2c: appi2c@8 {

reg = < 0x8 >;

label = "APPI2C";

};

};

//source code

#include <zephyr/drivers/i2c.h>

#define APPI2C_NODE DT_NODELABEL(appi2c)

static const struct i2c_dt_spec dev_i2c = I2C_DT_SPEC_GET(APPI2C_NODE);

int app_i2c_transfer(uint8_t slaveAddress, bool read_write, uint8_t *data, uint16_t size)

{

return read_write

? i2c_read(dev_i2c.bus, data, size, slaveAddress)

: i2c_write(dev_i2c.bus, data, size, slaveAddress);

}

I get communication errors very several times. (More than 50%)

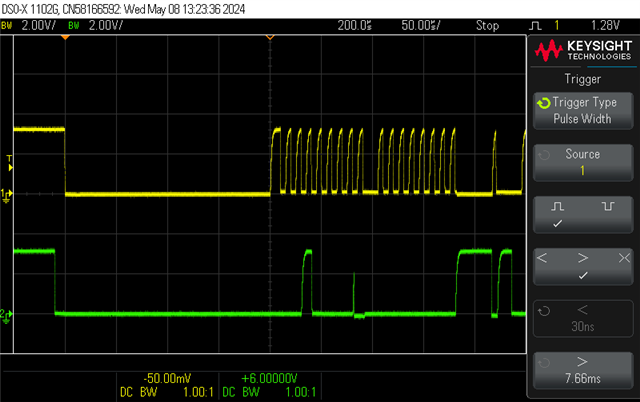

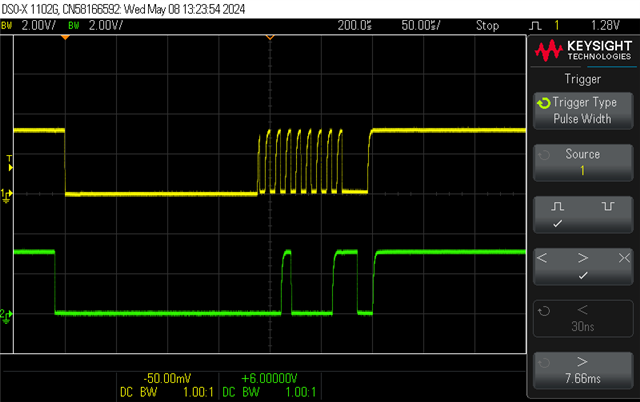

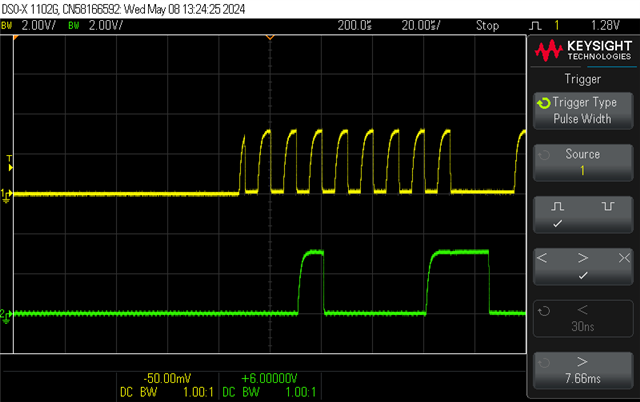

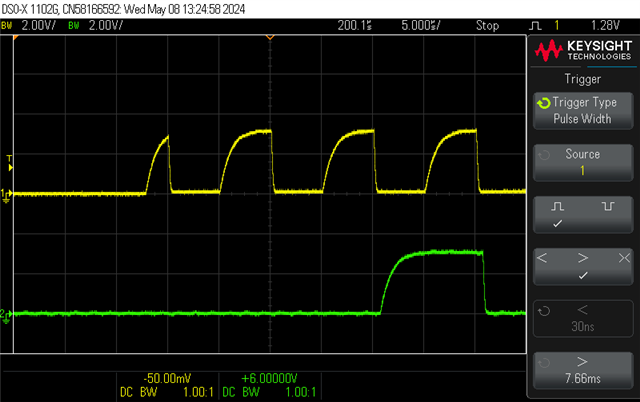

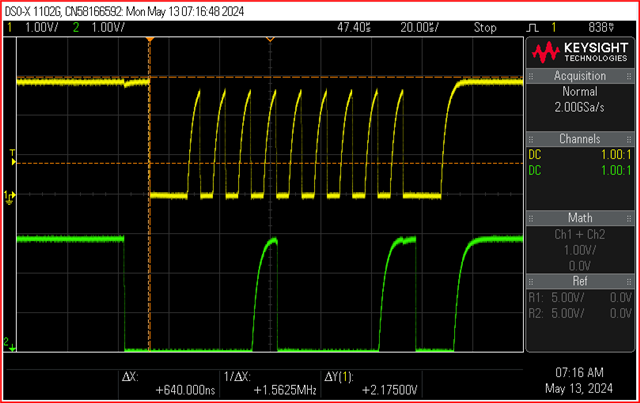

When the error occurs the first SCL impulse is half of the required. It's clear that at the beggining the slave is stretching the clock, but after releasing the master drives again too quickly.

The slave will nack the device address(0x08 in 7bit mode)

In 25% rate the communication is proper even to 256 bytes, but finally I got CRC error. For me this suggests that SDA is not sampled in the proper moment.

So my questions are:

- Does i2c driver api using a physical peripheral or emulates the lines by software?

- What kind of i2c errors can be detected by the api/driver? F.e. bus collision, timeout?

- What I do wrong, what I could do better?

Incidentally I use Texas Instrumet slave chip too (BQ76942) but I don't think it could be a problem.

It works properly with 3 other types of i2c master hardware:

- The original TI interface

- With an USB to I2C adapter controlled by .NET code

- With a Microchip PIC 8bit MCU

Thanks in advance,

Attila