Hi,

I encountered an issue from my custom board who are using a nrf52832.

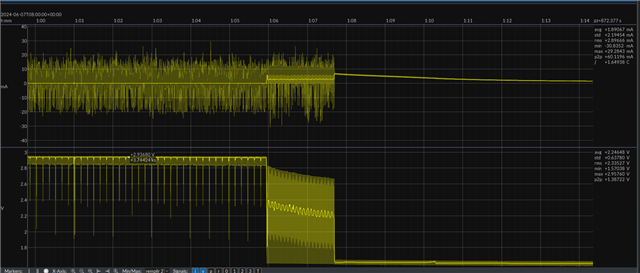

When i place my board in very cold temperature environment (around -35°C), sometimes the voltage drop below VBor, that put my device in reset state.

My issue are the voltage could stay below Vbor during long time (>15min), and the consumption is around 1-2mA against 20uA in running state. That reduce considerably my life time of my device.

Is this consumption normal (i don't found any information about this) ? Is there is a way to reduce it ?

I see some devzone that explain the best way is to use the POF in order to put the system-off mode before brown-out are detected. My issue are how to wake up the device from the system-off when the voltage are not critical ? In other way, how to wake up the device without human action ?

For information the battery use is a CR2450 with operating temperature -40 to 85 °C.

Thanks,

Best Regards,

Julien