Hello,

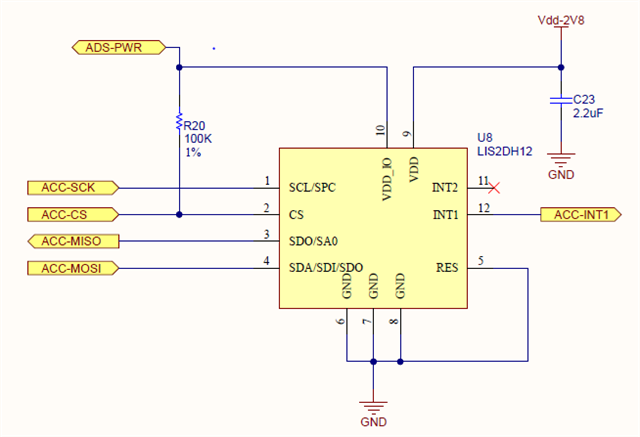

Our nRF52833 is powered through a load switch and control when to enable it is based on external peripherals logic. The MCU is connected to external peripherals that are ALWAYS powered ON and I am seeing what I think is leakage back into the MCU as I am measuring approx. 0.3V on the MCU coupling caps when its powered OFF. The MCU is connected to external IMU, EEPROM Memory, low power Accelerometers, and Hall sensors. All these external peripherals are connected via SPIM buses. Again, some of these are ALWAYS powered ON and some are only ON while the MCU is ON. the peripherals that are NOT always ON are also controlled via a load switch and their enable pin is controlled by the nRF52833.

I need to make sure the enable pin on the load switches of those peripherals that are disabled when the MCU is powered down are NOT floating. I do not want to use an external pull-down resistor as that would dramatically increase my power consumption when operating that sensor.

My question is: will the nRF52833 internal pull-downs remain when its load switch is DISABLED(no power going to it) as in the "system OFF mode" outlined in the datasheet?

also, any input on what happens to the peripherals that are always powered ON but their CS pin is either floating or pulled down as would be the case in this scenario when they operate on SPI Mode 0(CS is active when pulled low)?

In sum, power is my main concern and even placing 10M ohms pull downs is not sufficient for my design case.

your help will be greatly appreciated.

Regards,

Wael