Hi

We have an application in hardware development that requires multiple nRF5340 (PAN1783 modules) syncd together, so the I2S outputs can be input to an external DSP. The firmware will be based on the Nordic headset app.

The external DSP will run from an audio clock that is 12.288MHz or 24.576Mz to support the 48kHz only output. The DSP has inputs that only use the frame, bit clock and data, so the MCLK in is not a problem. But it is possible and likely that due to not being clocked from the same source the timing will drift over time and lose sync. For high quality audio we require all processors to be running from the same clock source for guaranteed timing, and even if the 32MHz system clock could divide down perfectly, it is still not as suitable for high quality audio as a low jitter clock source. So this leads to some questions.

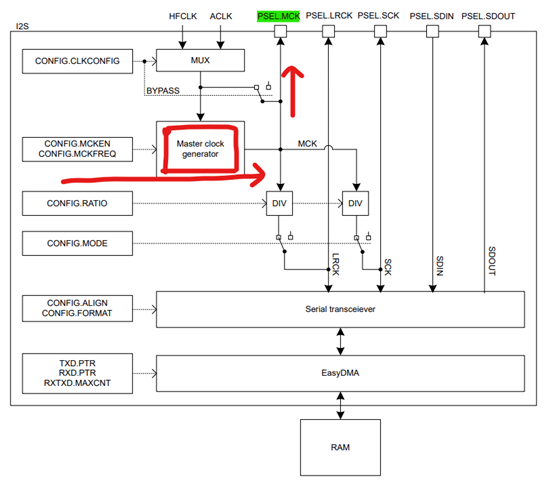

- I have looked at the I2S MCLK setup code for the V2.5.2 SDK and seen there is no easy way to change the MCLK to an input. Has this changed on the latest SDK or is it planned to?

- If the MCLK was an input, does the nRF5340 have the capability to run the I2S code from MCLK input? Or does this code only operate from the 32MHz system clock?

- Could the 32MHz system clock be replaced with a 24.576MHz clock? What would be the implications to the rest of the system especially the BLE-Audio?

Thanks in advance

Larry.