hello,

I need microsecond timer interrupts in my program, so I thought of using the TIMER of the hal library.

When I enable CONFIG_NRFX_TIMER0=y in prj.conf, the system starts up with an error.

When I enable CONFIG_NRFX_TIMER1=y, the system starts up normally without errors, but timer_event_handler does not execute normally.

#define TIMER_INST_IDX 1

static const nrfx_timer_t timer_inst = NRFX_TIMER_INSTANCE(TIMER_INST_IDX);

static void timer_handler(nrf_timer_event_t event_type, void * p_context)

{

if(event_type == NRF_TIMER_EVENT_COMPARE0)

{

LOG_INF("NRF_TIMER_EVENT_COMPARE0");

........

}

}

void timer_init(void)

{

IRQ_DIRECT_CONNECT(NRFX_IRQ_NUMBER_GET(NRF_TIMER_INST_GET(TIMER_INST_IDX)), IRQ_PRIO_LOWEST,

NRFX_TIMER_INST_HANDLER_GET(TIMER_INST_IDX), 0);

nrfx_err_t err;

nrfx_timer_config_t config = NRFX_TIMER_DEFAULT_CONFIG(NRFX_MHZ_TO_HZ(16UL));

config.bit_width = NRF_TIMER_BIT_WIDTH_32;

err = nrfx_timer_init(&timer_inst, &config, timer_handler);

if (err != NRFX_SUCCESS) {

LOG_ERR("Failed nrfx_timer_init, error: 0x%08X", err);

return ;

}

nrfx_timer_clear(&timer_inst);

uint32_t time_ms = 500;

uint32_t desired_ticks = nrfx_timer_ms_to_ticks(&timer_inst, time_ms);

nrfx_timer_extended_compare(&timer_inst, NRF_TIMER_CC_CHANNEL0, desired_ticks,

NRF_TIMER_SHORT_COMPARE0_CLEAR_MASK, true);

nrfx_timer_enable(&timer_inst);

NRFX_LOG_INFO("Timer status: %s", nrfx_timer_is_enabled(&timer_inst) ? "enabled" : "disabled");

}

When I add timer1-okay in the .overlay file, Cmake compilation fails

&timer1 {

status = "okay";

};

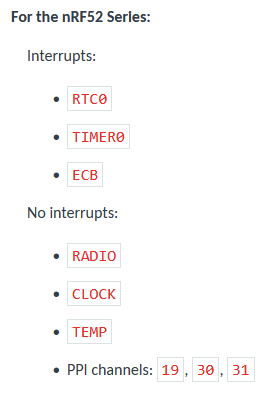

I don't know what hardware Zephyr and OpenThread occupy, can you explain it?

Regards,