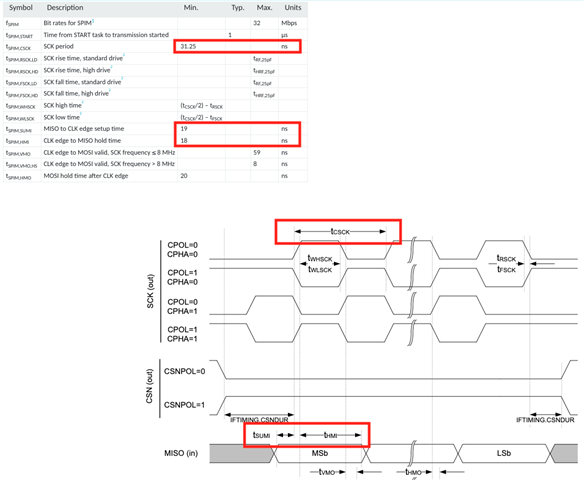

I am designing an FPGA to have a SPI slave port connected to the nRF5340 SPIM4 master running at 32 MHz. But the setup and hold times for this configuration are missing from the nRF5340 data sheet. The only setup and hold times are for the 8 MHz (125 nsec period) clock when using the other SPIM ports or not the dedicated high speed H0H1 ports P0.08-P0.12 for the SPIM4.

The setup and hold times for the slower ports are unworkable at 32 MHz, so I assume there have to be faster specs for the dedicated pins in high drive mode. Per the datasheet:

- tSPIM,SUMI (MISO to CLK edge setup time) = 19 nsec minimum

- tSPIM,HMI (CLK TO MISO hold time) = 10 nsec minimum

But since a 32 MHz clock has a period of 31.25 nsec, that leaves a very very tight window of 31 - (19 + 10) = only 2 nsec to make the signal transitions. This is not workable.

There must be shorter setup and hold requirements for SPIM4 with the higher speed dedicated pins. Can you tell me what the setup and hold times for MISO are?

--------

Similarly, the MOSI timing for the high speed SPIM4 port is missing. The "tSPIM,VMO CLK edge to MOSI valid, SCK frequency <= 8 MHz" is stated to be 59 nsec max, and it is made clear that that spec is for 8MHz and below. But then the line below that is for > 8 MHz, but the timing information is missing - just ".." where the numbers should be.

The MOSI hold time after CLK edge is given as 10 nsec, but that may also be different for the high speed pins.

These specs are important. We can't hook up a commercial chip, or our own FPGA design, to the SPIM4 at 32 MHz and guarantee the bus will work without these numbers.