Hi, I am a beginner into the embedded audio space, and happened upon this board to use for our university project. Our team's current plan would be to produce audio directly on the board and play it through the headphone jack, but have not found much success with the NRF5340 Audio application, as it has a lot of integration with Bluetooth (which we don't need for now). Right now we just need a simple application that plays a tune on the board.

In my search I have found the I2S echo application, which seems like a simple start for our use case. However, when trying to build the application we encountered the following error:

-- Found BOARD.dts: C:/ncs/v2.6.2/zephyr/boards/arm/nrf5340_audio_dk_nrf5340/nrf5340_audio_dk_nrf5340_cpuapp.dts

-- Found devicetree overlay: boards/nrf5340dk_nrf5340_cpuapp.overlay

devicetree error: pinctrl-names property in /soc/peripheral@50000000/i2s@28000 in C:/ncs/v2.6.2/zephyr/misc/empty_file.c has 1 strings, expected 2 strings

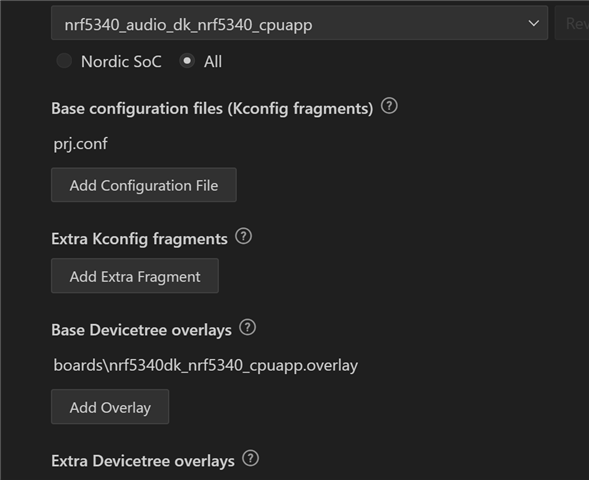

This is our build configuration (all other options left as default):

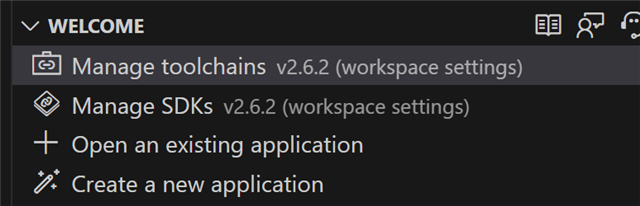

SDK version:

Any help would be appreciated! Thanks!