Hello!

I'm using the nRF5340 for a school design project and as such am financially limited to relatively low cost board manufacturers.

It seems that most of these manufacturers only support through vias (no blind/buried) and have a minimum hole size larger than what is used in the nRF5340 DK. Right now I am looking at JLCPCB as they can also do turnkey assembly

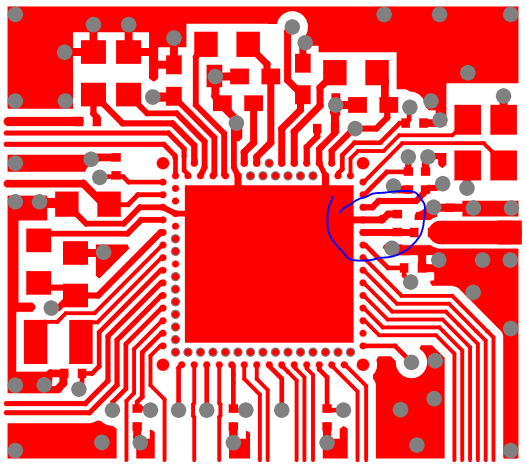

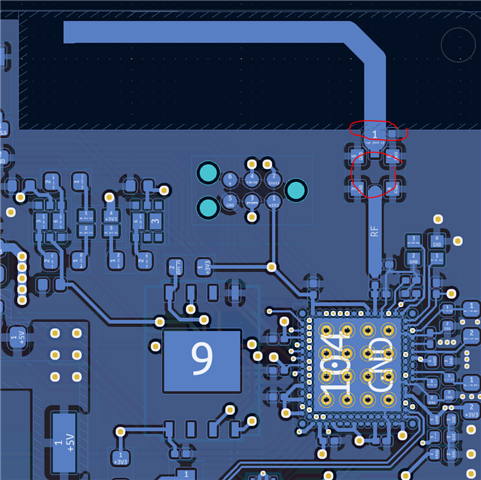

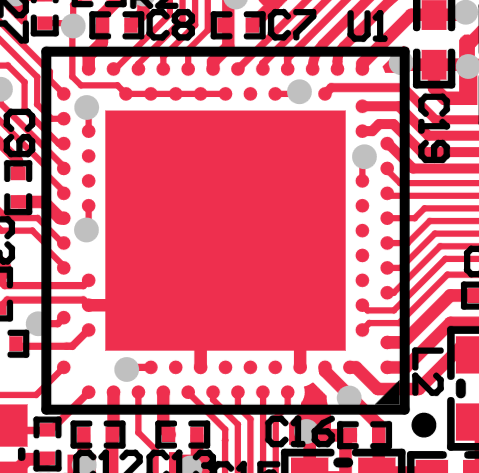

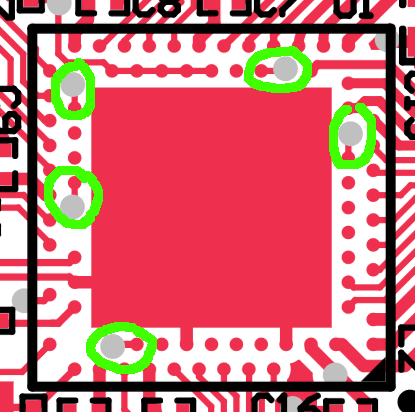

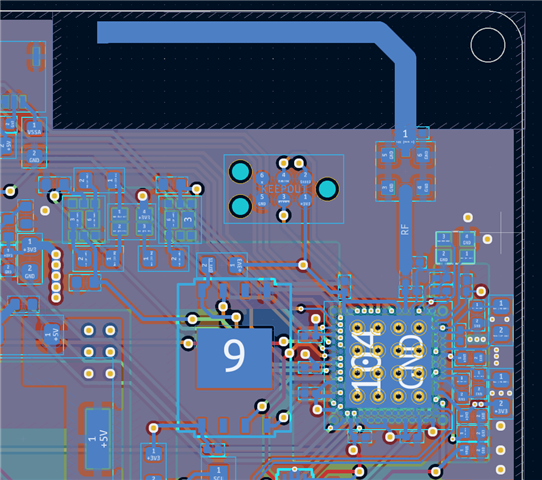

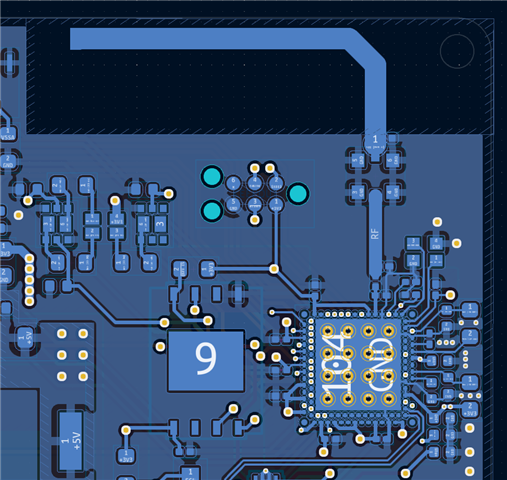

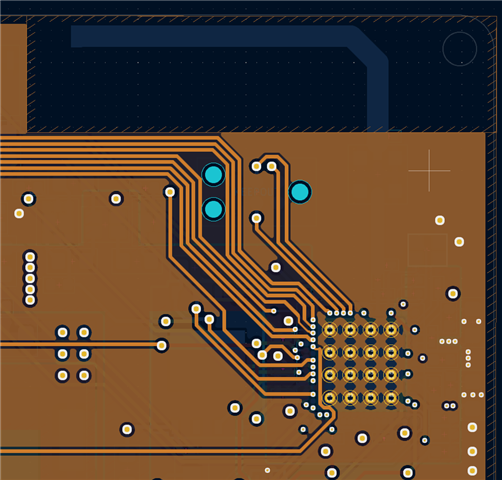

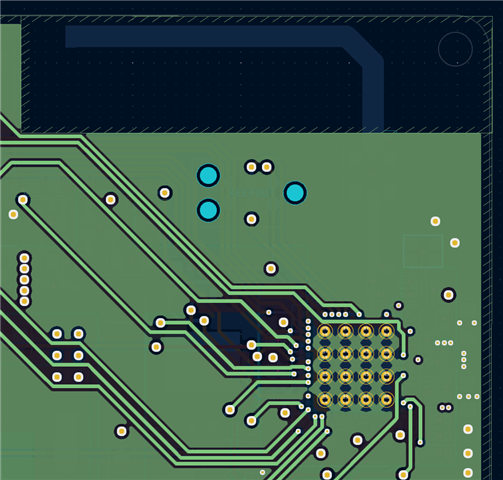

I mainly copied the layout from the DK, but have used the smallest vias I could for breaking out the inner pins and some of the outer ones. Current via specs are through vias with a hole size of 0.15mm and with a 0.3mm diameter. For reference the DK uses a 0.1mm hole size with 0.3mm diameter.

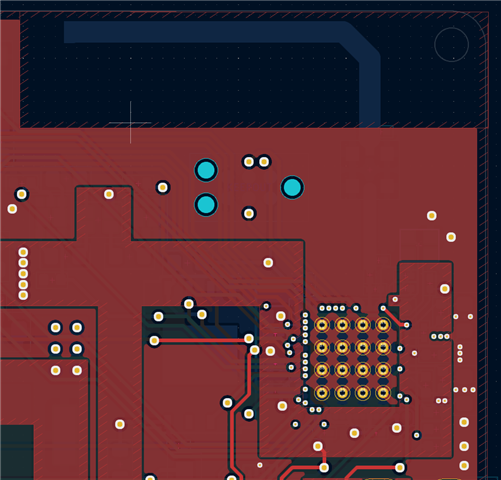

What are the odds that this hole size will work for connecting these pads? Screenshot of my current layout below (feel free to provide general layout criticism if there's anything of note, never worked on a project this dense before)

Images:

Any help would be very much appreciated!