Hi!

I'm working on the firmware part that needs to perform operations on the same variables both inside GPIO IRQ and the software timer callback.

So, there is a need for a critical section to make sure they operate properly.

By looking through the documentation, I found that I can use "irq_lock()"/"irq_unlock()" to achieve this (software timer implementation also makes use of these under the hood), but I found that after calling irq_lock(), GPIO interrupts are not locked.

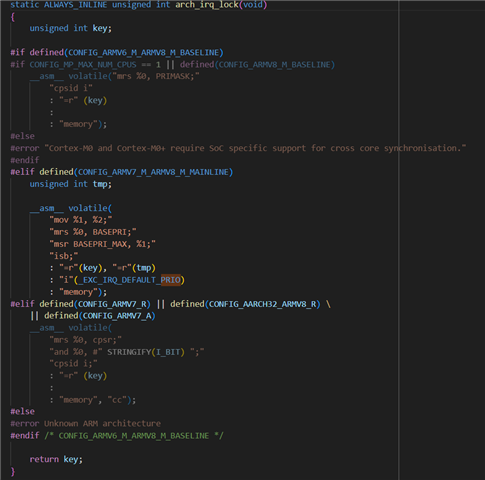

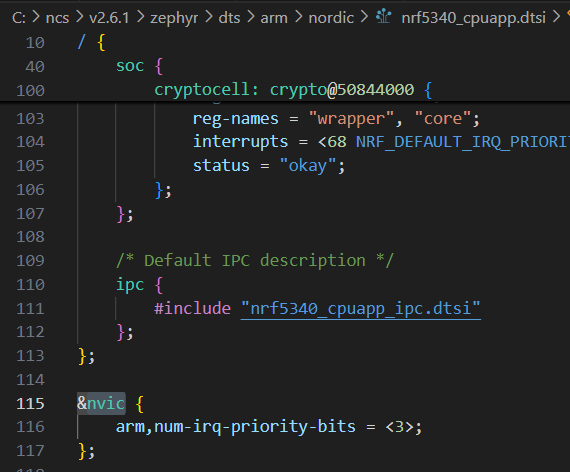

Diving deeper into the "lock()" implementation, I found the following:

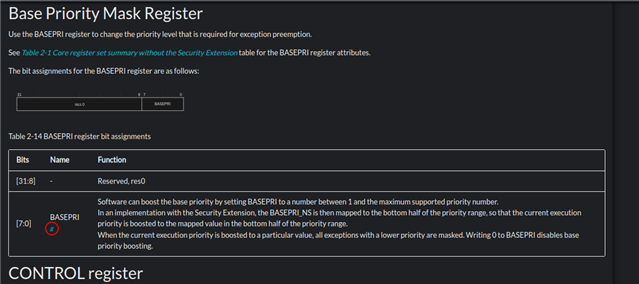

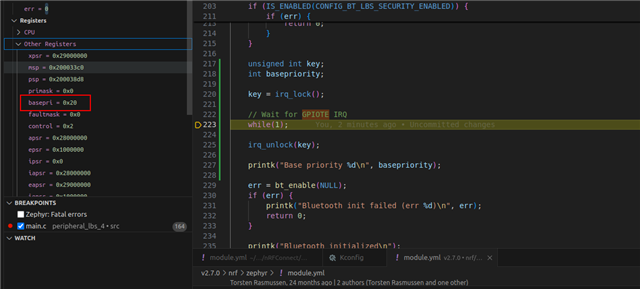

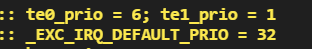

So, BASEPRI register is set with the value 32 (_EXC_IRQ_DEFAULT_PRIO).

So, all priorities higher than 32 (numerically lower) can generate interrupts while the code is insiode this critical section.

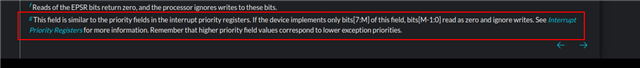

According to the *.dts config, "NUM_IRQ_PRIO_BITS" is set to 3, so lowest IRQ priority possible should be 8.

With default configuration, the priority for the GPIO interrupts are 6 (got this value by calling "NVIC_GetPriority(GPIOTE0_IRQn").

Therefiore, it looks like "irq_lock()" does not disable any interrupts.

That is why I need to call something like "irq_disable(GPIOTE0_IRQn)" to explicitly disable GPIO interrupts for the time of processing.

Am I missing something here or is it correct behaviour for the "irq_lock()"?

Thanks,

Anton