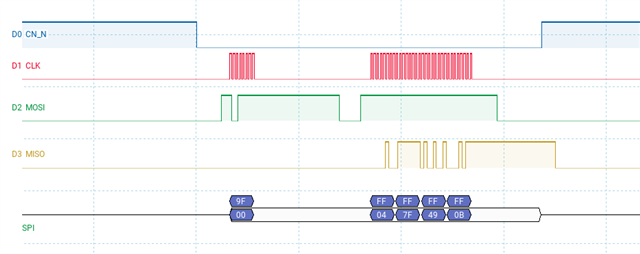

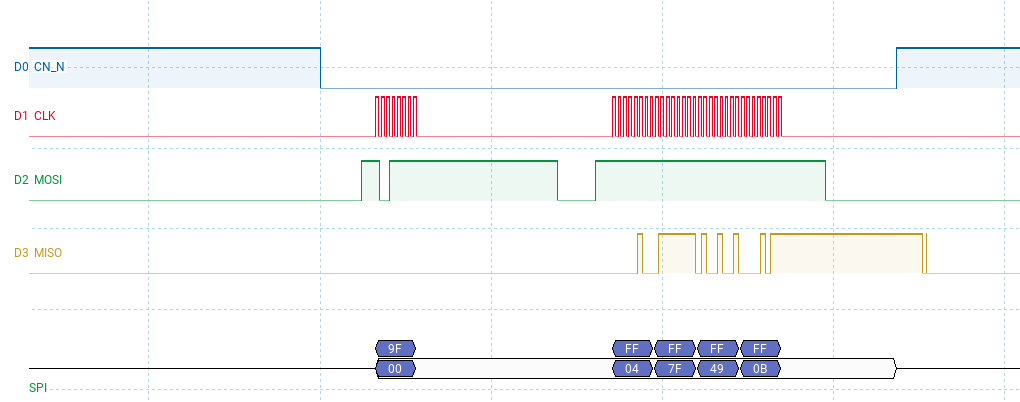

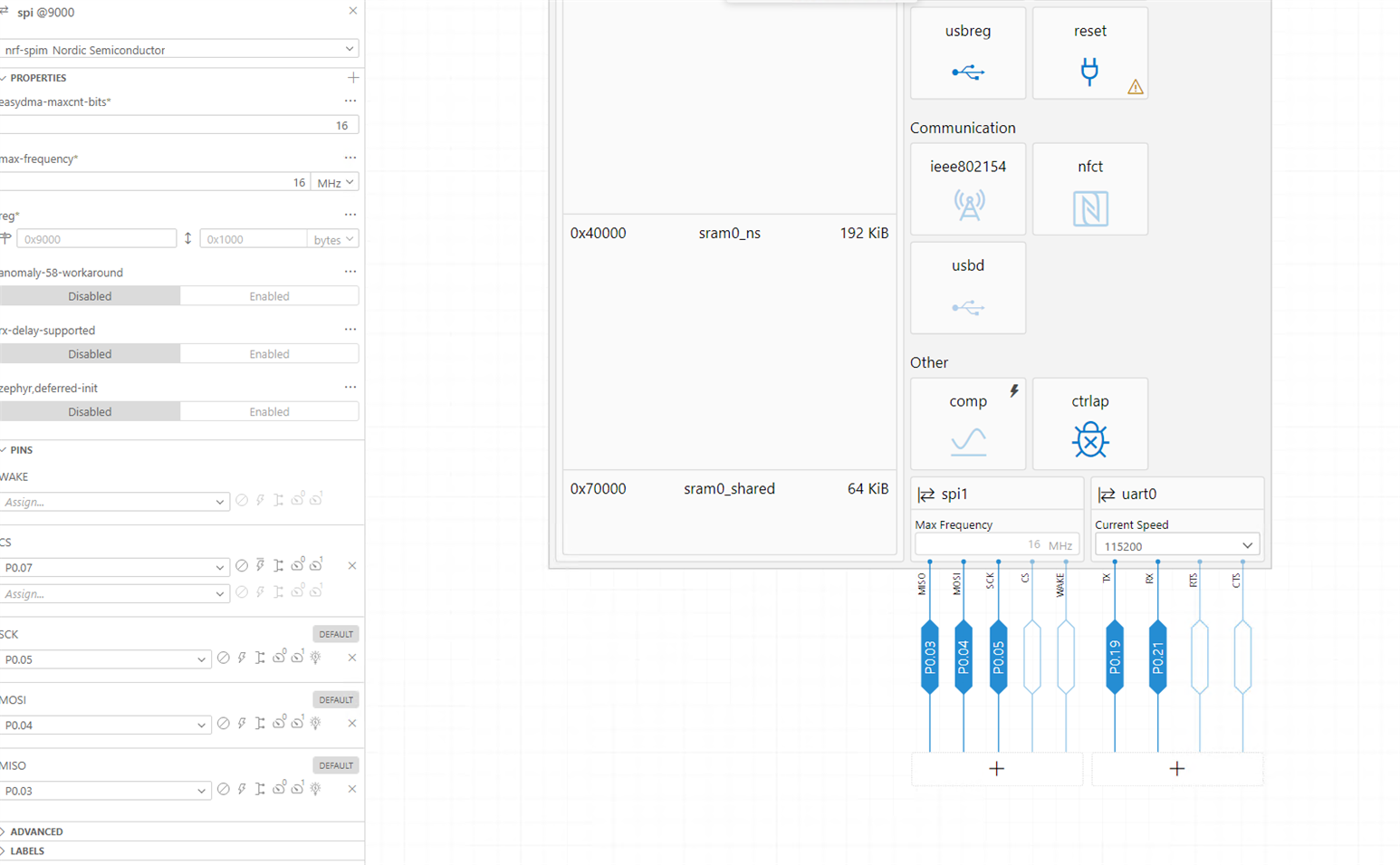

I/ trying to read the ID of a Fijitsu FRAM type MB85RS4MT using the Nordic device nRF5340. I can properly initialize the SPI and transmit the RDID =0x9F command. The FRAM returns, what I think is the proper ID, but it won't show up in software. I'm using the synchronous spi_transceive routine. I Initialize the ID buffer prior use with all 0xFF. The data is overwritten with all zeros ?. This is how the DTC and code looks like. I'm really stuck, can it have something to do with double use of GPIOs ???? within the Device Tree visual editor it appears that NFC is disabled (also using pin P0.03). Could it be that the NFC part it somehow blocking proper use of the pins for SPI. (How can I check?)

The code looks as follows:

______________________________________________________________________________________________________________________________

So id[4] is overwritten with all zeros????

I really don't understand what is going on. Note that all connections between the FRAM and nRF are straight forward. Checked the print layout and stuff.