Hi,

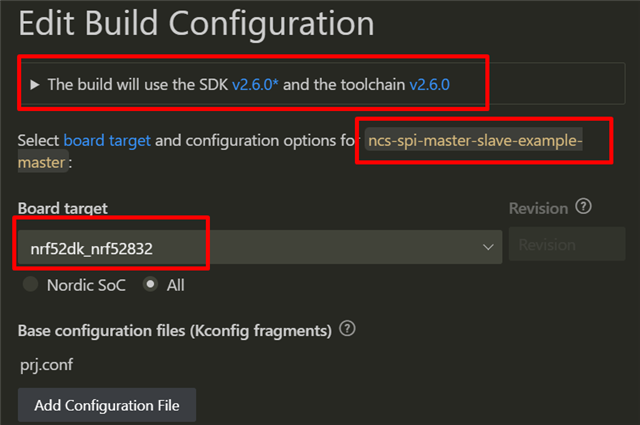

I am trying establish connection between SPI MASTER and SPI SLAVE on two boards nRF52 DK. I am using example "ncs-spi-master-slave-example" SPI Master/Slave example

SDK v2.6.0, Toolv2.6.0

pin connections:

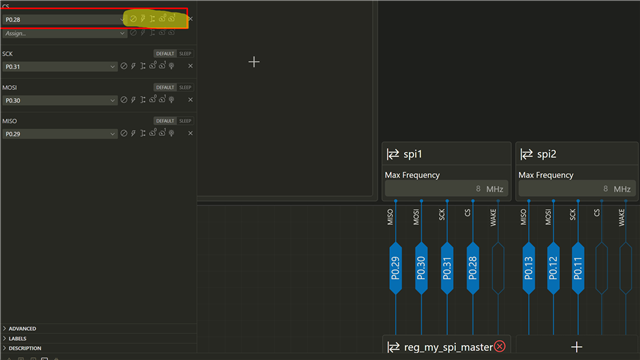

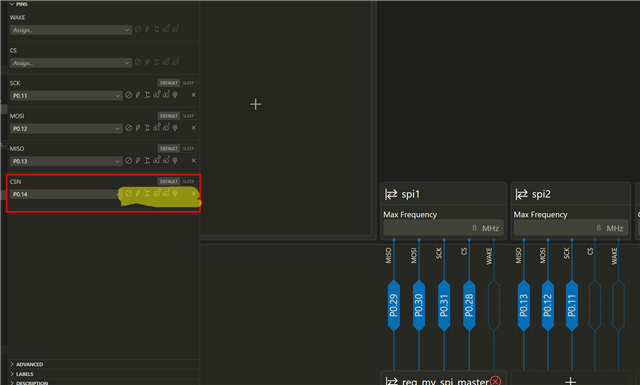

master board: slave board:

MOSI: P0.30 ---> P0.12

MISO: P0.29 <--- P0.13

SCLK: P0.31 ---> P0.11

CS/CSN:P0.28 ---> P0.14

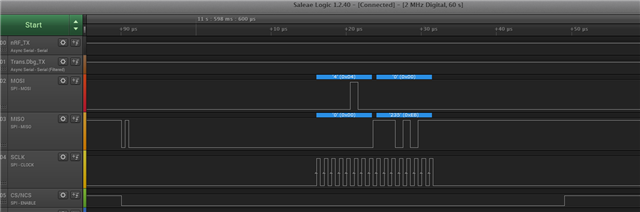

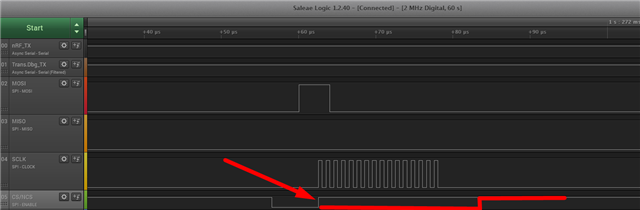

When the SPI Master activates the CS pin and attempts to start communication, CS will be turned off at the same time as the first clock appears. This will cause the transmission to fail.

Do you have any idea what this could be? I'm attaching a log from the logic analyzer.

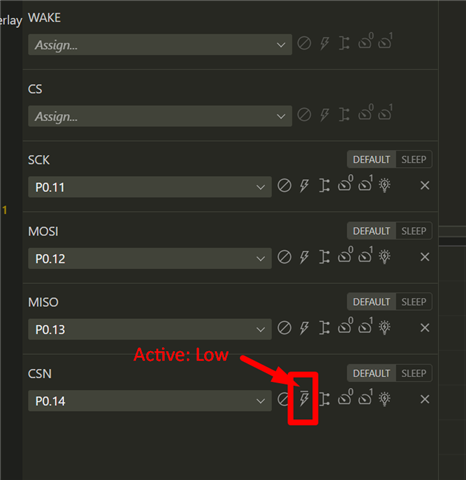

I tried changing the CSN to Active:Low, but without success.

My second question is whether this example works on a single board (if the appropriate pins are connected).

Martin