Hi!

I'm trying to portnRF7002 QSPI bus driver for one of the NXP MCUs. Communication with nRF7002 under Zephyr is already established and everything works as expected.

Driver port is nearly finished, but I have issues with making sure that QSPI transfer for PP4 and READ4 meets nRF7002 requirements.

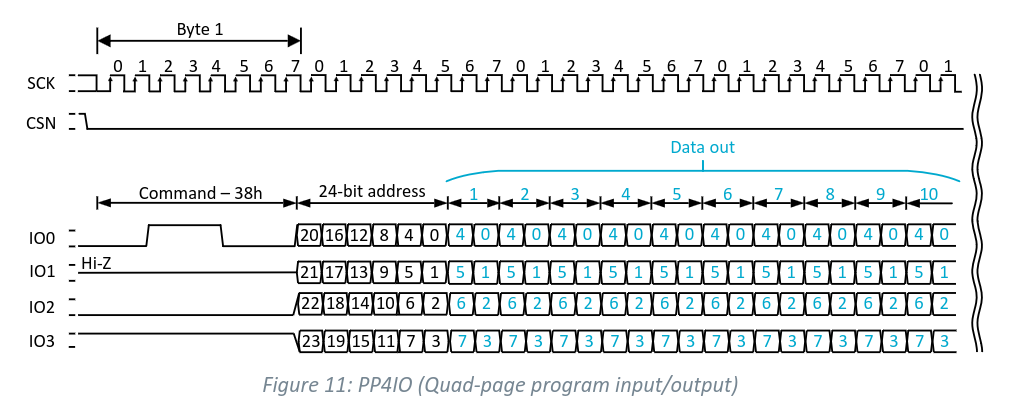

From the datasheet (nRF7002_PS_v1.1.pdf):

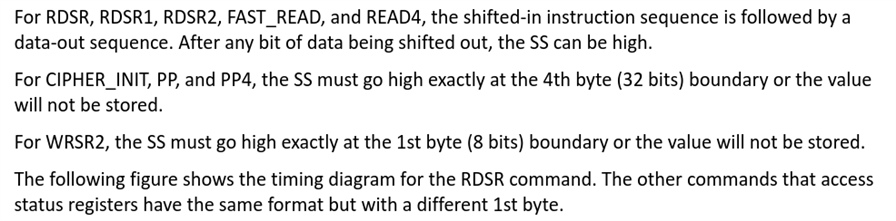

- Figure 9 shows, that during 4-dummy bits IO3 is high. Is this required, or just to show that IO lines state does not matter?

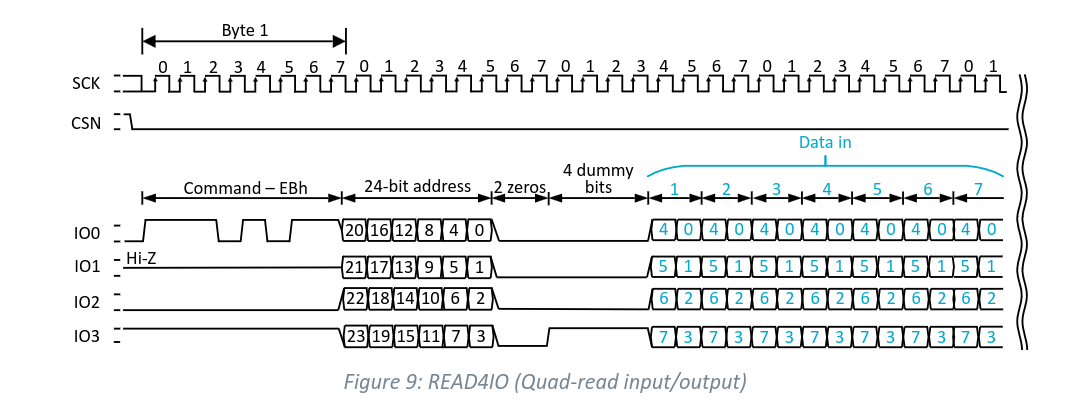

- Based on the figure 11 I assume, that the mentioned 4th byte boundary is about Data out bytes?

- If the 4th byte condition is not met, is the whole operation not valid or is only last partial 32-bit part dropped?

QSPI peripheral that is available seems to be somewhat limited regarding cycles not equal to 8 clock cycle. I am looking for some workaround, based on nRF7002 tolerance for not perfect QSPI transactions.