*EDIT* - Using NCS 2.9

I am using the QSPI peripheral to communicate with a display.

1. I initialize the QSPI peripheral. I have tried both blocking and non-blocking. Both return successfully.

//ret = nrfx_qspi_init(&config, NULL, NULL);

ret = nrfx_qspi_init(&config, nrfx_qspi_handler, NULL);

if (ret != NRFX_SUCCESS)

{

LOG_ERR("Error writing to QSPI");

}

2.) I attempt to read or write to the QSPI peripheral.

- I get two different errors.

Blocking Mode - this gives me the "NRFX_TIMEOUT" error.

Non-Blocking Mode - No error

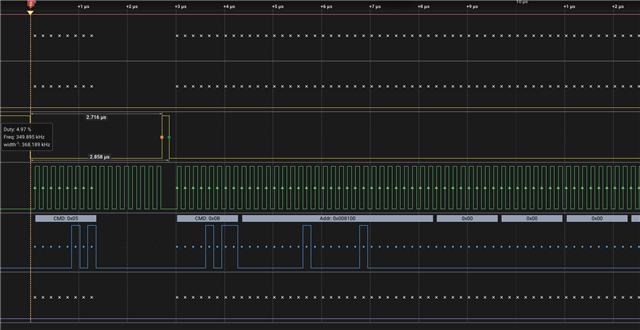

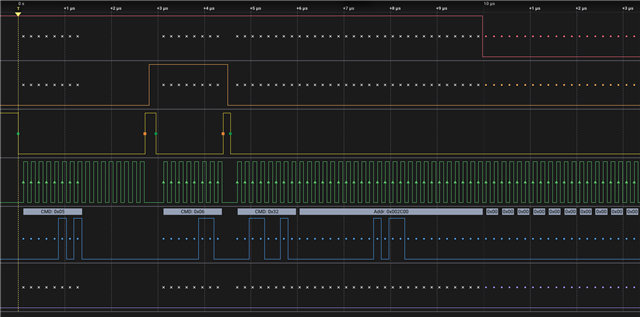

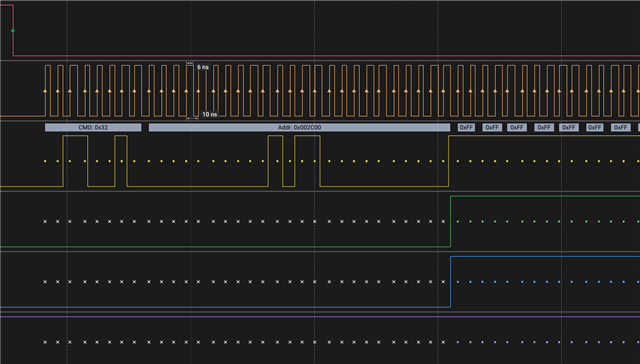

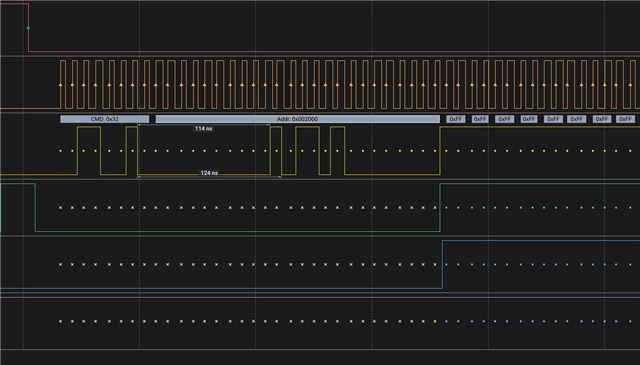

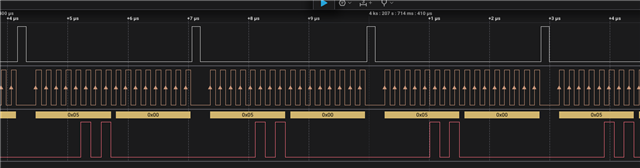

A logic analyzer shows both methods continuously transmitting data. It does not just transmit/read the specified number of bytes.

I have made sure my buffers are word aligned.

uint8_t read_data[16] = {0};

ret = nrfx_qspi_read(read_data, 16, LCD_SET_REG_ADDRESS(0x81));

if (ret != NRFX_SUCCESS)

{

LOG_ERR("Error reading from QSPI %s", nrfx_error_string_get(ret));

}

LOG_HEXDUMP_INF(read_data, 16, "Read data");

k_sleep(K_MSEC(100));

is_tx_done = false;

uint32_t address = 0x80 << 8;

uint8_t cmd[4] = {0}; //__attribute__((aligned(4)))

cmd[0] = 0x1;

ret = nrfx_qspi_write(cmd, sizeof(cmd), address);

if (ret != NRFX_SUCCESS)

{

LOG_ERR("Error writing to QSPI, err = %s", nrfx_error_string_get(ret));

}

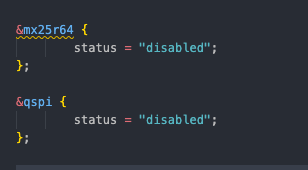

3.) Overlay - I have tried disabling the QSPI or the flash for the nrf5340dk overlay. Neither of these changes the behavior.

4.) Clock - I must call nrf_clock_hfclk192m_div_set(NRF_CLOCK, NRF_CLOCK_HFCLK_DIV_1) before reading or writing or I get an NRFX_ERROR_FORBIDDEN error.

This is due to the NRF53_ERRATA_159_ENABLE_WORKAROUND below.

if (qspi_errata_159_conditions_check())

{

return NRFX_ERROR_FORBIDDEN;

}

static bool qspi_errata_159_conditions_check(void)

{

#if NRF_CLOCK_HAS_HFCLK192M && NRF53_ERRATA_159_ENABLE_WORKAROUND

if ((nrf_clock_hfclk192m_div_get(NRF_CLOCK) != NRF_CLOCK_HFCLK_DIV_1) ||

(nrf_clock_hfclk_div_get(NRF_CLOCK) != NRF_CLOCK_HFCLK_DIV_2))

{

return true;

}

else

#endif

{

return false;

}

}

I have tried disabling this workaround in may CMakeFile.txt with target_compile_definitions(app PRIVATE NRF53_ERRATA_159_ENABLE_WORKAROUND=0), however, this does not seem to work. Is there a correct way to disable this workaround?

I would like to run from a 128Mhz HFCLK, but this seems to cause issues.

5. Prj - Here are my PRJ file configs. I have attempted to disable QSPI NOR features.

CONFIG_NRFX_QSPI=y

CONFIG_SPI_NOR=n

CONFIG_NORDIC_QSPI_NOR=n # Enable SPI NOR flash support

CONFIG_PINCTRL=y

Any ideas on a solution to allow the QSPI peripheral to function correctly? I am concerned the NRFX QPSI is conflicting with the device tree QSPI settings. Or perhaps I am missing critical configuration settings for the QSPI peripheral to allow it to read and write.