The workaround says:

"Trigger TASKS_PLLSTART before TASKS_XOSTART is triggered and trigger TASKS_PLLSTOP after TASKS_XOSTOP is triggered."

I would like to start HFXO using DPPI. According to Errata 39 I must make sure PLL is running at any time HFXO is running if understand correctly.

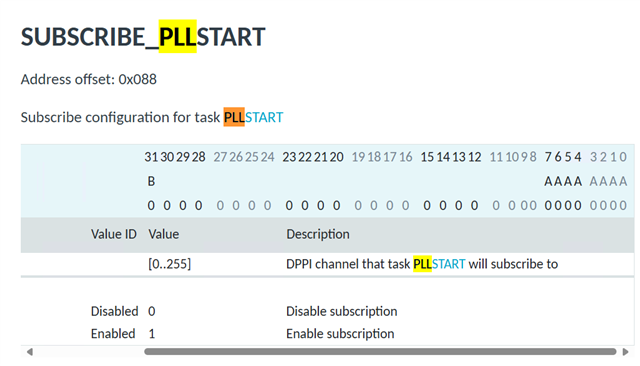

Question: can I subscribe PLLSTART to the same DPPI channel as XOSTART so they are both started at the same time and that will satisfy the Errata 39 or must I make sure PLLSTART is triggered a bit before? If the first option is not ok but only the second option, how many microseconds (or nanoseconds) earlier? Would one single 16 MHz cycle be enough? And same question about XOSTOP and PLLSTOP. The number of DPPI channels in the low power domain is extremely limited (4) so it would be nice if XOSTART and PLLSTART could share the same channel.

Thanks!