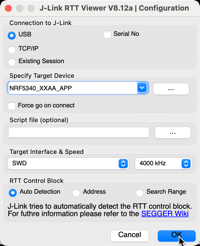

I am trying to flash a new board using a Segger J-Link Plus Compact. I use the same code to flash my nRF5340DK and it runs fine. I see the debug statements in the JLinkRTTViewer: I have a board definition which is building and can flash the board:

Flashing build_4 to 000000000 west flash -d /Users/zzzzzz/Projects/GitHub/yyyyy/hello_world_sysbuild/build_4 --dev-id 000000000 -- west flash: rebuilding [0/10] Performing build step for 'hello_world_sysbuild' ninja: no work to do. [1/10] Performing build step for 'mcuboot' ninja: no work to do. [4/10] cd /Users/zzzzz/Projects/GitHub/yyyyy/hello_world_sysbuild/build_4/_sysbuild && /opt/nordic/ncs/toolchains/b8efef2ad5/Cellar/cmake/3.21.0/bin/cmake -E true [6/9] No install step for 'mcuboot' [7/9] Completed 'mcuboot' [8/9] cd /Users/zzzzz/Projects/GitHub/yyyyy/hello_world_sysbuild/build_4/_sysbuild && /opt/nordic/ncs/toolchains/b8efef2ad5/Cellar/cmake/3.21.0/bin/cmake -E true -- west flash: using runner nrfjprog -- runners.nrfjprog: reset after flashing requested -- runners.nrfjprog: Flashing file: /Users/zzzzz/Projects/GitHub/yyyyy/hello_world_sysbuild/build_4/merged.hex [ #################### ] 5.137s | Erase file - Done erasing [ #################### ] 1.050s | Program file - Done programming [ #################### ] 1.011s | Verify file - Done verifying Applying pin reset. -- runners.nrfjprog: Board with serial number 000000000 flashed successfully.

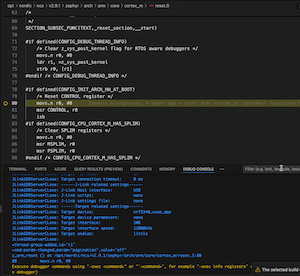

I have set the board using the jlinkexe:

SEGGER J-Link Commander V8.12a (Compiled Jan 9 2025 14:39:08) DLL version V8.12a, compiled Jan 9 2025 14:38:28 Connecting to J-Link via USB...O.K. Firmware: J-Link V11 compiled Dec 4 2024 17:53:35 Hardware version: V11.00 J-Link uptime (since boot): 0d 00h 00m 53s S/N: 000000000 License(s): RDI, FlashBP, FlashDL, JFlash, GDB USB speed mode: High speed (480 MBit/s) VTref=3.300V (fixed) J-Link>Power On J-Link>ShowHWStatus VTref=3.300V (fixed) ITarget=6mA TCK=0 TDI=0 TDO=0 TMS=0 TRES=1 TRST=0 Supported target interface speeds: - 180 MHz/n, (n>=12). => 15000kHz, 13846kHz, 12857kHz, ... - Adaptive clocking J-Link>ShowHWStatus VTref=0.000V TCK=0 TDI=0 TDO=0 TMS=0 TRES=0 TRST=0 Supported target interface speeds: - 16 MHz/n, (n>=4). => 4000kHz, 3200kHz, 2666kHz, ... J-Link>

I also don't see the device in the nRF Connect iOS app like I do with the nRF5340DK. I'm not sure how I debug this?