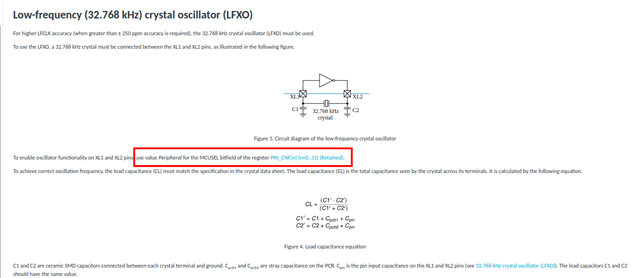

Our design has an nRF5340 with RV3028C7 to provide the 32 kHz clock via P0.00.

If I configure P0.00 as a digital input, I can see the pin toggling.

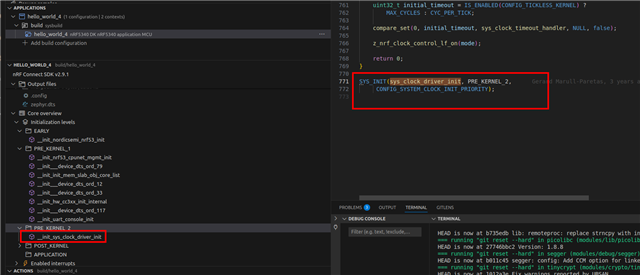

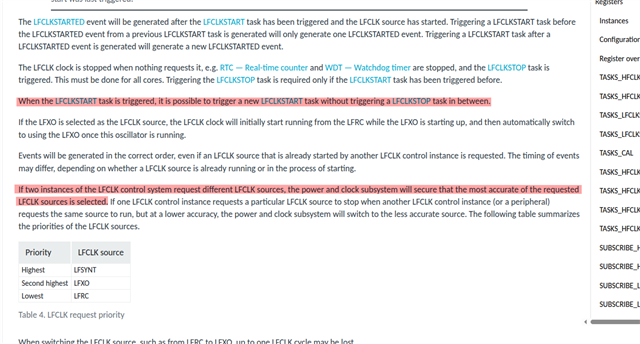

However, if I use the code below to try and switch from to the external clock, the EVENTS_LFCLKSTARTED doesn't happen. Any idea why this would be?