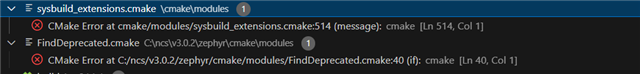

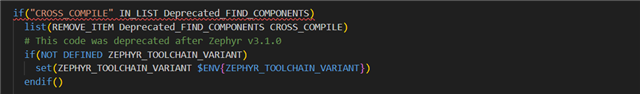

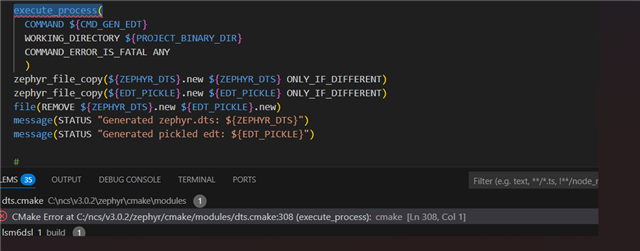

when I try to build a code for integrating sensor in nRF 5340 dk, this error comes, I tried even after installing cmake manually from the cmake website https://cmake.org/, but unable to solve these errors , kindly help with a suitable solution.

SDK version 3.0.2