Hello all,

I am using the nrf52840 MCU and NCS v2.6.2 for my application development. Here I am using SPIM3.

I am using a peripheral which have an internal FIFO. From that peripheral, I receive the interrupt when the FIFO is full. I received the interrupt every 160ms and read 360 bytes of data. It uses a fixed register read/write cycle every interrupt for the FIFO read. This process is successful over the longtime. After some random point in time SPI driver sent the wrong value sequence, and due to that, my peripheral internal configuration changed, and it stopped working as per expectations.

-

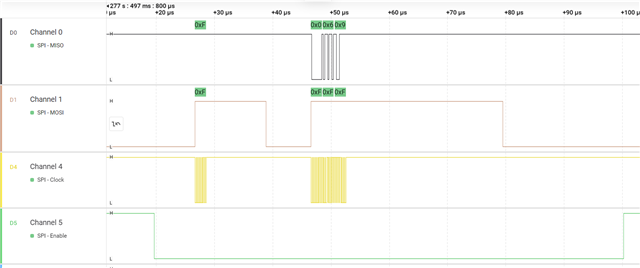

A successful send sequence of 4 bytes is 0xFF,0xFF,0xFF,0xFF.

- Found wrong sequence of 4 bytes is 0x00,0xFF,0xFF,0xFF. After this sequence peripheral goes into failure.

If I swap the SPIM2 and SPIM3. The issue is not reproduced, and the peripheral is working fine.

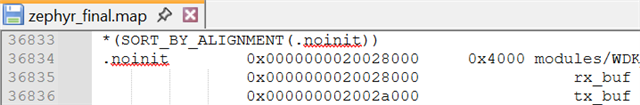

I found the errata document(section 3.29) from nrf web. In that mention, like the tx pointer corruption issue, sometimes, when the CPU accesses the same memory. That causes this issue. I am researching the same, and I found CONFIG_NRF52_ANOMALY_198_WORKAROUND, CONFIG_NRFX_SPIM3 as a part of the solution. This config is already turned on, still I am still facing the same issue.

Can anyone help me with the SPIM3 issue?

Thanks,

Dinkar