I got a 52840-DK a couple of days ago. I installed the latest IAR Embedded Workbench (9.70.1); also downloaded the latest Nordic SDK,and then started building and executing some of the included examples. I started with "blinky",then one from ble, and I was able to get the first 3-4 examples working. Then I tried "timer" and it failed with "The processor has attempted to execute an undefined instruction (CFSR.UNDEFINSTR)"

Tried a couple more examples and they all failed with the same error, so I went back to blinky and tried to run it anew. However, this time even blinky failed with the above error.

Looked into the output and found these:

Fri Jul 04, 2025 00:51:55: Auto speed detection, JTAG speed is set to: 1000 kHz

Fri Jul 04, 2025 00:51:55: Warning: Timeout while erasing sectors @0x00000000, RAMCode did not respond in time!

Fri Jul 04, 2025 00:51:55: Failed to erase sectors.

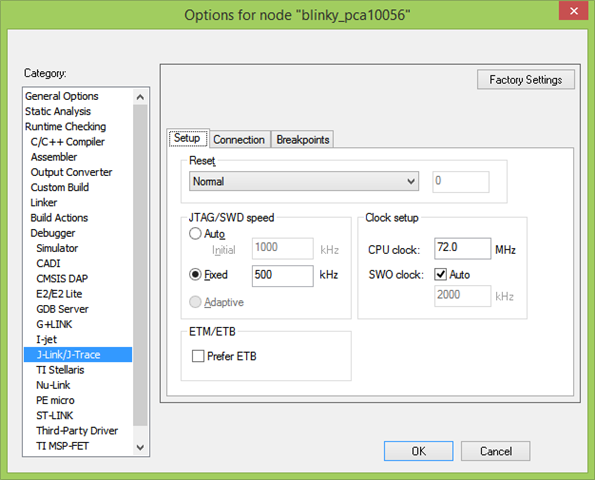

Thinking that reducing speed could help, I looked for an option to manually lower the JTAG speed, but could not find one. (Note: I'm not much of an expert on EWB)

Any idea on what exactly causing this and how to fix it? I know that flash can fail, but I probably had less than a dozen total download attempts when the failures started, and I didn't do anything until I realized what was happening. Subsequently, I powercycled/reconnected the board several times and restarted EWB to no avail.

System is Win 8.1 x64, IAR embededd 9.70.1, the SDK is: nRF5_SDK_17.1.0_ddde560, board is connected via USB and I've tried both onboard (2.0) and ad-in card (3.0) ports

Full log:

Fri Jul 04, 2025 00:51:54: IAR Embedded Workbench 9.70.1 (C:\Dev\ewarm-9.70.1\arm\bin\armproc.dll)

Fri Jul 04, 2025 00:51:54: Loaded macro file: C:\Dev\ewarm-9.70.1\arm/config/debugger/NordicSemi/nRF52_PROT.dmac

Fri Jul 04, 2025 00:51:54: Loaded macro file: C:\Dev\ewarm-9.70.1\arm/config/debugger/NordicSemi/nRF52_2.dmac

Fri Jul 04, 2025 00:51:54: Evaluation license - IAR Embedded Workbench for Arm, Evaluation Edition 9.70

Fri Jul 04, 2025 00:51:54: J-Link library version: 84800

Fri Jul 04, 2025 00:51:54: JLINK command: ProjectFile = C:\Dev\nRF52840\nRF5_SDK_17.1.0_ddde560\examples\peripheral\blinky\pca10056\blank\iar\settings\blinky_pca10056_nrf52840_xxaa.jlink, return = 0

Fri Jul 04, 2025 00:51:54: Device "NRF52840_XXAA" selected.

Fri Jul 04, 2025 00:51:54: DLL version: V8.48 , compiled Jul 2 2025 12:03:07

Fri Jul 04, 2025 00:51:54: Firmware: J-Link OB-SAM3U128-V2-NordicSemi compiled Oct 9 2024 11:00:56

Fri Jul 04, 2025 00:51:54: Serial number: 683966735

Fri Jul 04, 2025 00:51:54: Selecting SWD as current target interface.

Fri Jul 04, 2025 00:51:54: JTAG speed is initially set to: 1000 kHz

Fri Jul 04, 2025 00:51:54: InitTarget() start

Fri Jul 04, 2025 00:51:54: InitTarget() end - Took 7.14ms

Fri Jul 04, 2025 00:51:54: Found SW-DP with ID 0x2BA01477

Fri Jul 04, 2025 00:51:54: DPIDR: 0x2BA01477

Fri Jul 04, 2025 00:51:54: CoreSight SoC-400 or earlier

Fri Jul 04, 2025 00:51:54: Scanning AP map to find all available APs

Fri Jul 04, 2025 00:51:54: AP[2]: Stopped AP scan as end of AP map has been reached

Fri Jul 04, 2025 00:51:54: AP[0]: AHB-AP (IDR: 0x24770011, ADDR: 0x00000000)

Fri Jul 04, 2025 00:51:54: AP[1]: JTAG-AP (IDR: 0x02880000, ADDR: 0x01000000)

Fri Jul 04, 2025 00:51:54: Iterating through AP map to find AHB-AP to use

Fri Jul 04, 2025 00:51:54: AP[0]: Core found

Fri Jul 04, 2025 00:51:54: AP[0]: AHB-AP ROM base: 0xE00FF000

Fri Jul 04, 2025 00:51:54: CPUID register: 0x410FC241. Implementer code: 0x41 (ARM)

Fri Jul 04, 2025 00:51:54: Found Cortex-M4 r0p1, Little endian.

Fri Jul 04, 2025 00:51:54: FPUnit: 6 code (BP) slots and 2 literal slots

Fri Jul 04, 2025 00:51:54: CoreSight components:

Fri Jul 04, 2025 00:51:54: ROMTbl[0] @ E00FF000

Fri Jul 04, 2025 00:51:54: [0][0]: E000E000 CID B105E00D PID 000BB00C SCS-M7

Fri Jul 04, 2025 00:51:54: [0][1]: E0001000 CID B105E00D PID 003BB002 DWT

Fri Jul 04, 2025 00:51:54: [0][2]: E0002000 CID B105E00D PID 002BB003 FPB

Fri Jul 04, 2025 00:51:54: [0][3]: E0000000 CID B105E00D PID 003BB001 ITM

Fri Jul 04, 2025 00:51:54: [0][4]: E0040000 CID B105900D PID 000BB9A1 TPIU

Fri Jul 04, 2025 00:51:54: [0][5]: E0041000 CID B105900D PID 000BB925 ETM

Fri Jul 04, 2025 00:51:54: Reset type: NORMAL (wiki.segger.com/J-Link_Reset_Strategies)

Fri Jul 04, 2025 00:51:54: Reset: Halt core after reset via DEMCR.VC_CORERESET.

Fri Jul 04, 2025 00:51:54: Reset: Reset device via AIRCR.SYSRESETREQ.

Fri Jul 04, 2025 00:51:54: Hardware reset with strategy 0 was performed

Fri Jul 04, 2025 00:51:54: Initial reset was performed

Fri Jul 04, 2025 00:51:54: Loaded debugee: C:\Dev\nRF52840\nRF5_SDK_17.1.0_ddde560\examples\peripheral\blinky\pca10056\blank\iar\_build\blinky_pca10056.out

Fri Jul 04, 2025 00:51:55: Auto speed detection, JTAG speed is set to: 1000 kHz

Fri Jul 04, 2025 00:51:55: Warning: Timeout while erasing sectors @0x00000000, RAMCode did not respond in time!

Fri Jul 04, 2025 00:51:55: Failed to erase sectors.

Fri Jul 04, 2025 00:51:55: 1606 bytes downloaded (6.65 Kbytes/sec)

Fri Jul 04, 2025 00:51:55: Download completed.

Fri Jul 04, 2025 00:51:55: Reset type: NORMAL (wiki.segger.com/J-Link_Reset_Strategies)

Fri Jul 04, 2025 00:51:55: Reset: Halt core after reset via DEMCR.VC_CORERESET.

Fri Jul 04, 2025 00:51:55: Reset: Reset device via AIRCR.SYSRESETREQ.

Fri Jul 04, 2025 00:51:55: Software reset was performed

Fri Jul 04, 2025 00:51:55: Target reset

Fri Jul 04, 2025 00:51:55: Memory map 'after startup completion point' is active

Fri Jul 04, 2025 00:51:55: HardFault exception.

Fri Jul 04, 2025 00:51:55: The processor has escalated a configurable-priority exception to HardFault.

Fri Jul 04, 2025 00:51:55:

Fri Jul 04, 2025 00:51:55: An MPU or Execute Never (XN) default memory map access violation has occurred on an instruction fetch (CFSR.IACCVIOL, MMFAR).

Fri Jul 04, 2025 00:51:55:

Fri Jul 04, 2025 00:51:55: The processor has attempted to execute an undefined instruction (CFSR.UNDEFINSTR).

Fri Jul 04, 2025 00:51:55:

Fri Jul 04, 2025 00:51:55: Exception occurred at PC = 0x5d4, LR = 0xffffffff

Fri Jul 04, 2025 00:51:55:

Fri Jul 04, 2025 00:51:55: See the call stack for more information.