Hello,

I'm developing with an nRF54L15 Revision 1 (QFAA-B00). I'm encountering a problem described in the errata:

3.4 [8] SPIM: Wrong data is transmitted on MOSI

(Symptom: When SPIM is used with CPHA=0, prescaler > 2, and the first bit to transmit is '1', the data on MOSI is incorrect).

I am using Zephyr (nRF Connect SDK v3.0.2) and the SPI API (spi_transceive_dt() from <zephyr/drivers/spi.h>).

I have confirmed that the workaround is executed:

USE_WORKAROUND_FOR_ANOMALY_NRF54L_8_NRF54H_212 is defined in the NRFX driver (nrfx_spim.c), and the code performs the actions described in the errata:

- Sets CSNDUR to (prescaler / 2 + 1)

- Writes 0x82 to the SPIM register at offset 0xc84 before starting the transfer

- Resets this register to 0x00 after EVENTS_STARTED

However, even with this workaround active, the first bit problem persists:

- On the oscilloscope, the MOSI line only transitions to ‘1’ on the rising edge of SCK instead of being centered between clock edges

- As a result, the slave samples the wrong value for the first bit if it is ‘1’.

- This behavior only affects the first 8-bit word after each CSN (SS) activation, and only if the first bit is '1'.

My configuration:

- Custom board, nRF54L15 Revision 1 (QFAA-B00), also tested with Engineering B (QFAA-BB0) – same issue

- SPI frequency: 2 MHz (prescaler = 64)

- SPI mode 0 (CPOL=0, CPHA=0)

- Using instance SPIM00

- Zephyr nRF Connect SDK v3.0.2

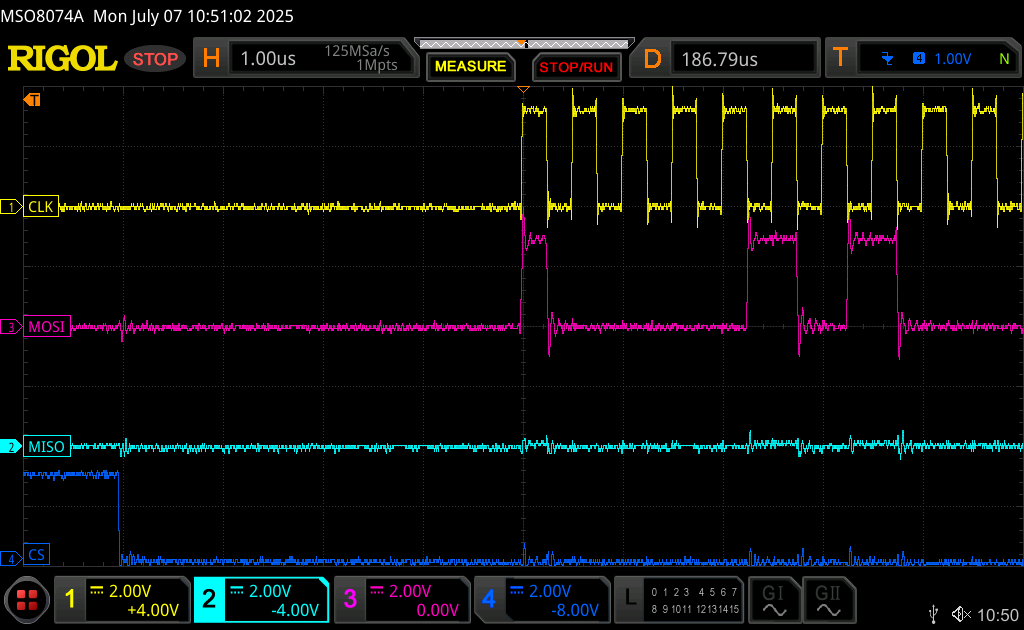

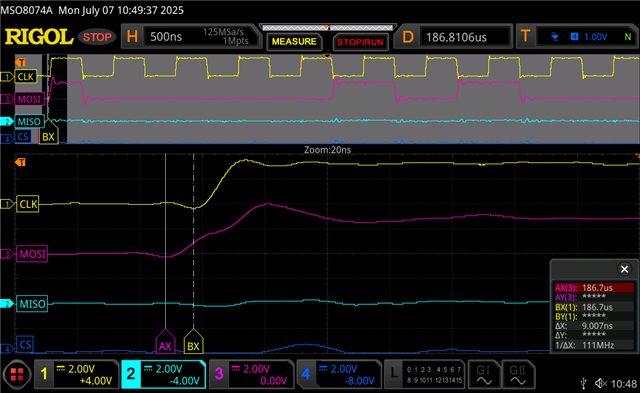

Oscilloscope captures:

The first bit transitions to ‘1’ on the rising edge of SCK instead of being centered between clock edges

Can you confirm if anything else is required on the application (or configuration) side to ensure the workaround is fully effective when using Zephyr’s SPI API? Are there any known limitations or further steps to handle this errata in this context?

Thank you for your support,

Baptiste