Hello,

We are currently evaluating a very low power application using the nRF5340+7002. Our hardware design includes a complex power supply configuration, and we need to interface the nRF5340 with 3.3V GPIO levels while potentially using a lower VDDH supply.

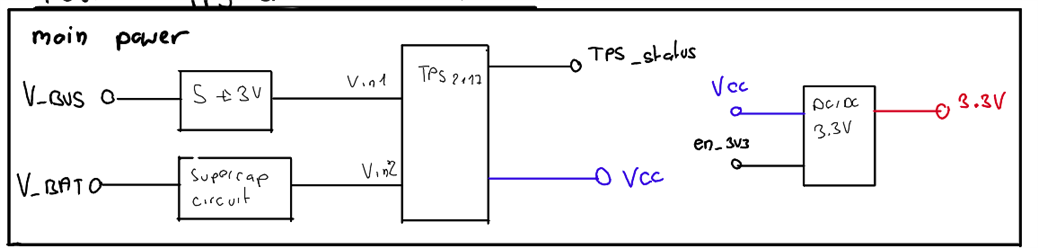

Example of our Power Supply Configuration:

- TPS2117 for switching between USB (with 3V regulator) and Vbat (supercap system)

- VCC in battery mode: 2.7V to 2.4V (depending on battery level)

- Host + WiFi connection in High Voltage Mode

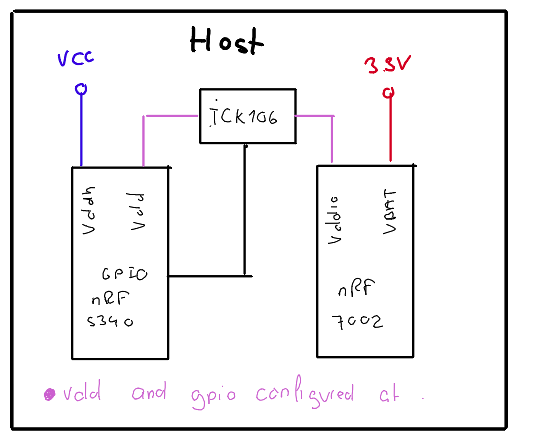

- VCC directly powers the nRF5340

- VREG powers VDD and IOVDD of the 7002

- 7002 is powered by 3.3V rail controlled by the 5340

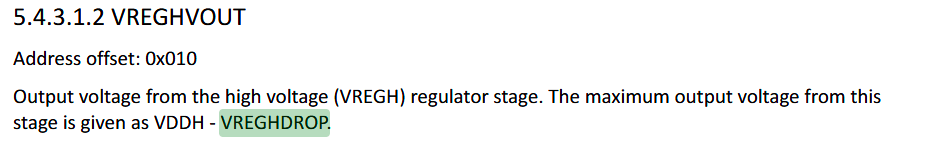

Requirements: We need to configure GPIO levels with VREGHVOUT at 3.3V to control other board components. However, since VCC ranges from 2.7V to 2.4V, this appears impossible in LDO mode due to the constraint: "The maximum output voltage from this stage is given as VDDH - VREGHDROP."

Questions:

- If we configure VREG in DC/DC mode instead of LDO mode, is it possible to achieve VREGHVOUT = 3.3V with a lower VDDH?

- An alternative approach would be to connect the nRF5340 to 3.3V instead of VCC, switching to 3.3V only when needed and using VCC with passthrough on the 3.3V regulator for all other cases. Will the nRF5340 tolerate the voltage drops and spikes during VCC to 3.3V transitions since the core works at 1.2V?

Thank you in advance for your assistance.

Best regards,

Valentin Künti