Hello,

I am trying to optimize performance of a series of SPIM transactions using the 5340. Each transaction is 3 bytes long: CSN goes low, clock out 3 bytes, CSN goes high. Only the 3 received bytes matter here, the transmitted bytes are ignored. I want to minimize the turnaround time between transactions so that I can maximize the number of transactions per second.

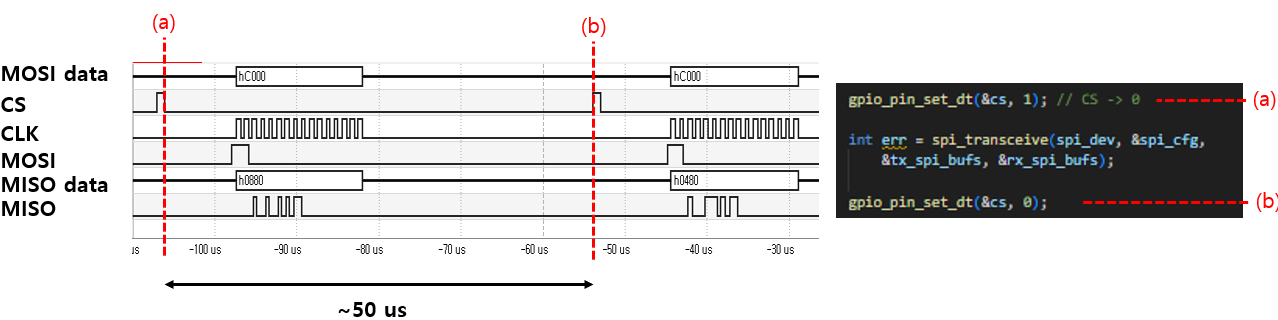

I implemented a test using the 5340 DK and the NRFx driver, with SPIM 4 set up at 16 MHz with hardware CSN control. The SPIM END/START short is set, so as soon as one transaction completes the next begins. This should minimize turnaround time, since each transaction is started via DPPI and no CPU involvement is needed (in fact, for this test the CPU is put to sleep after kicking off the first SPI transaction). This seems to work as expected, transferring data from the sensor continuously.

However, I am seeing that there is a significant delay between the completion of one SPI transaction and the start of the next - approximately 900 ns. I am wondering what this turnaround delay is attributable to and whether there's anything I can do to reduce or eliminate it.

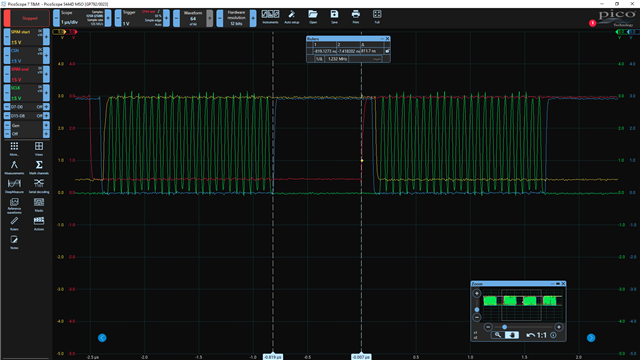

To get a better idea of what the SPIM peripheral is doing, I connected the SPI STARTED event to one GPIOTE task (toggle) and SPIM END event to another GPIOTE task (also toggle). Then, scoped these lines plus CSN and SCLK. An example capture is below. You can see there is an ~800 ns delay between CSN going high and the SPIM END event, which is larger than I expected. It's not pictured here, but I also measured the timing of the SPIM ENDRX event, which is 125 ns before the SPIM END event.

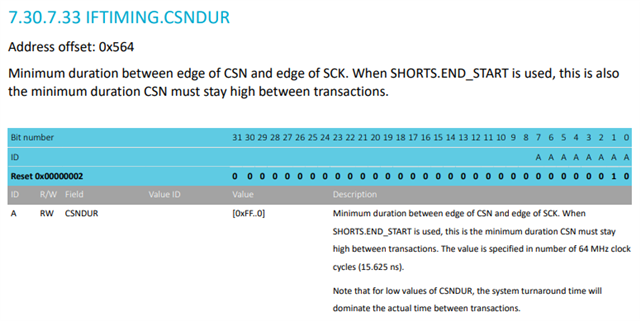

I found in the 5340 product spec that "for low values of CSNDUR, the system turnaround time will dominate the actual time between transactions". But, no mention of what the system turnaround time is or whether it can be influenced. In my case CSNDUR is set to 2, so it is only ~4% of the observed delay. I thought maybe the DMA is transferring the final byte into RAM during this time, but would have expected that to run much more quickly than ~800 ns.

My questions are:

1. Is there any more info on what the "system turnaround time" is, or where it comes from?

2. What causes the 125 ns delay between SPIM ENDRX and SPIM END? Is there any way to remove this portion of the overall delay? Note that END is not delayed to the Tx event, since 0 bytes are transmitted (I confirmed ENDTX occurs at the beginning of the transfer at the same time as the STARTED event).

3. Is there any other way to reduce the turnaround time between transactions?

4. I noticed from the scope capture that the SPIM STARTED event appears to occur after the CSN line goes low (~30 ns to be specific). I would have thought Is this expected? I'm not sure if this is an artifact of the DPPI signal propagation or if the CSN line going low actually precedes the STARTED event.

Thanks for your help!