Hello,

I am new to embedded programming and I'm trying to create a small application that uses BT advertisements.

I've tested my code on an NRF52840 dongle, and a board with an NRF52810 chip.

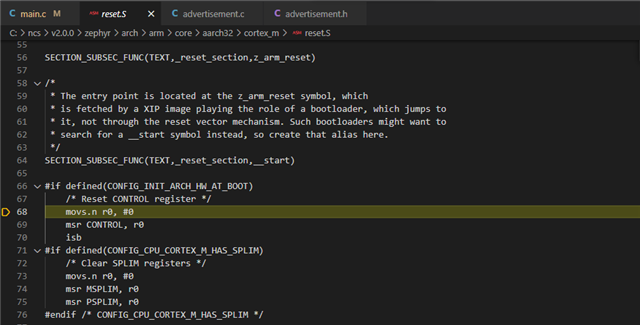

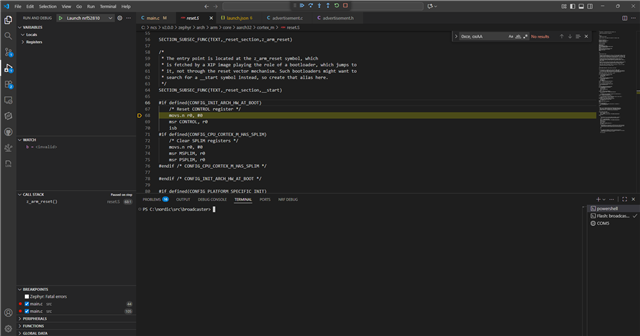

In a few cases, when trying to debug my code on either a board with an NRF52810 or an NRF52832, the debugger breaks immediately on \v2.0.0\zephyr\arch\arm\core\aarch32\cortex_m\reset.S

Trying to step over or continue just leads the debugger to hang, and it seems like the application doesn't continue to run.

With the NRF52810, just trying again the next day suddenly worked. I'm not able to get the NRF52832 working though.

Could this be a hardware issue (I've had some of these boards laying around for a while)? Or is it some other problem with my setup?

Thanks for your help!