Hello,

We have a dual-purpose connection in our design where the signal can be either an analog input or a digital output. We have done some testing and can see that we can switch between the two functions to get the desired affect, but it complicates a few aspects of FW. We are considering connecting two connections: the analog connection and a GPIO.

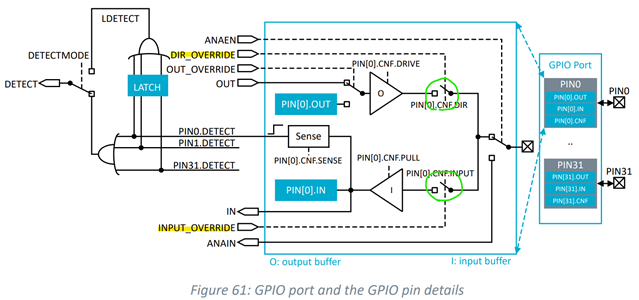

Is there a GPIO state (perhaps input, buffer disconnected) where the GPIO interface tolerates mid-rail voltages, is "very high" high impedance (10Mohm or is at least known to calibrate the math), and is easy to reconfigure as an output?

Thanks!